# ATLAS SCT READOUT AND BARREL MACRO-ASSEMBLY TESTING AND DESIGN OF MAPS TEST STRUCTURES

### Bruce Joseph Gallop

Thesis submitted to

The University of Birmingham

for the degree of Doctor of Philosophy

Particle Physics Group School of Physics and Astronomy University of Birmingham

September 2005

## Abstract

The semiconductor tracker sub-detector of the ATLAS experiment consists of 4088 individual silicon detector modules. A data acquisition system, SctRodDaq, required to configure, read out and test these modules both during large scale assembly and in the final experimental setting was designed, and is described here. SctRodDaq is shown to function well during assembly of the first stage of the SCT, Barrel 3.

The design and layout of pixel test structures to further the development of Monolithic Active Pixel Sensors for particle physics applications is described. Preliminary test results of the device show promise though they demonstrate the requirement of a relatively thin epitaxial layer for particle detection applications.

## **Author's Contribution**

The ATLAS SCT, as for other modern high energy physics experiments, is the work of a large number of contributors.

A large part of my work was in the production of software for the SCT DAQ system using the final read-out hardware described in chapter 4 and known as SctRodDaq. This is the work of several people and is based upon the previous SCTDAQ software. The SCTDAQ software existed, though I contributed substantially to its stability and long term monitoring. For use during SCT module production at RAL I contributed to the development and maintenance of a web-based database system

Though the design of SctRodDaq was the work of the group, the implementation of each of the individual components was done by one or two individuals. My particular work on SctRodDaq was the development of the low-level SctApi software, described in section 4.8, and the configuration database, described in section 4.13, both essential parts. Low-level classes to access the ROD, BOC, TIM and VME drivers were written by others, to some of which I made minor contributions. Much effort was spent with many iterations of the ROD firmware and hardware, understanding its interactions with real SCT modules, and debugging problems.

The results described in chapter 5 demonstrate the first use of this software in a large scale setting. The analysis is the work mainly of others, though with much interaction

with the central software. This is a clear demonstration of the viability of read-out for the full SCT system.

The final chapter describes a separate piece of work motivated by the author's background of a first degree in electronics: the results of part-time work carried out to develop new pixel system. My work is the layout of the 9 different pixels. The support electronics, submission and testing were the work of others.

Though not described in the following, I have spent some time at CERN working on the use of SCTDAQ for SEU tests in the irradiations programme and to a lesser extent for the system test and test beams. I was also present at CERN to help with the use of SctRodDaq in the ATLAS combined test beam.

## Acknowledgements

First, I would like to acknowledge the supervision of Peter Phillips, Dave Charlton and Richard Apsimon.

For the SCT I would like to thank everyone involved in the irradiations, system tests and beam tests at CERN; barrel module assembly at RAL; and barrel macro-assembly at Oxford. Particular mention should go to Matt, Alan, Peter and John for discussions about SctRodDaq. Paul, Chris, Lars and Gareth for welcome to CERN and helping get to know the hardware. Gareth again for putting me up on a visit to CERN at short notice. Douglas for keeping unusual hours working on the ROD DSP code from across the Atlantic.

Work on MAPS was greatly helped by discussions with Giulio, Renato, Jaap, Arwell and Mike.

Both education and entertainment were gleaned from coffee breaks, lunches and dinners at Birmingham, CERN and RAL. Particularly everyone at Staff House and the Brass Band. Also, Sian, Kelly and John for suggestions of other things to do.

Finally, thanks to my family for all their support and I'm sorry Gran isn't around to see the finished article.

# Contents

| 1        | Intr | oduction 1                                 |

|----------|------|--------------------------------------------|

|          | 1.1  | The Standard Model                         |

|          |      | 1.1.1 The Higgs Boson                      |

|          |      | 1.1.2 Proton-proton Colliders              |

|          | 1.2  | Silicon Detectors                          |

|          |      | 1.2.1 Interaction of Particles with Matter |

|          |      | 1.2.2 Silicon Detectors                    |

|          |      | 1.2.3 p-n Junctions                        |

|          |      | 1.2.4 Effects of Radiation in Silicon      |

|          | 1.3  | Summary                                    |

| <b>2</b> | Dot  | ector Overview 15                          |

| _        | 2.1  | LHC                                        |

|          | 2.2  | ATLAS                                      |

|          | 2.2  | 2.2.1 Co-ordinate system                   |

|          |      | 2.2.2 Particle Detection                   |

|          |      | 2.2.3 Triggers                             |

|          |      | 2.2.4 ATLAS Overview                       |

|          | 2.3  | Inner Detector                             |

|          | ۷.5  | 2.3.1 Pixels                               |

|          |      | 2.3.2 Semi-Conductor Tracker               |

|          |      | 2.3.3 TRT                                  |

|          |      | 2.3.4 Track Reconstruction                 |

|          | 2.4  |                                            |

|          | 2.4  | v                                          |

|          |      | 8                                          |

|          | 2.5  | -                                          |

|          | 2.5  | Muon Detector                              |

|          |      | 2.5.1 Toroids                              |

|          | 0.0  | 2.5.2 Detector Chambers                    |

|          | 2.6  | The ATLAS Data Acquisition System          |

|          | 2.7  | Summary                                    |

| 3 | SC                | Hardware 4                                                     | 0        |

|---|-------------------|----------------------------------------------------------------|----------|

|   | 3.1               | SCT Infrastructure                                             | 10       |

|   |                   | 3.1.1 SCT Cooling System                                       | 13       |

|   |                   | 3.1.2 SCT Power Supplies                                       | 13       |

|   | 3.2               |                                                                | 14       |

|   |                   | 3.2.1 Binary read-out                                          | 14       |

|   |                   | 3.2.2 Electrical Specifications                                | 15       |

|   | 3.3               | SCT Module Overview                                            | 16       |

|   |                   | 3.3.1 Silicon Detectors                                        | 18       |

|   |                   | 3.3.2 Baseboard                                                | 19       |

|   |                   | 3.3.3 Hybrid                                                   | 19       |

|   |                   | 3.3.4 SCT Read-out Chip Overview                               | 50       |

|   |                   | 3.3.5 Module Optical Read-out and Control                      | 56       |

|   | 3.4               | Off-Detector SCT Read-out Hardware                             | 57       |

|   |                   | 3.4.1 TIM                                                      | 59       |

|   |                   | 3.4.2 BOC                                                      | 59       |

|   |                   | 3.4.3 ROD                                                      | 32       |

|   | 3.5               | Summary                                                        | 8        |

| 4 | A T-              |                                                                |          |

| 4 | A L<br>ules       | ata Acquisition and Characterisation System for ATLAS SCT Mod- | 9        |

|   | 4.1               |                                                                | 9<br>59  |

|   | $\frac{4.1}{4.2}$ |                                                                | 79<br>72 |

|   | 4.2               |                                                                | 72       |

|   |                   | ·                                                              | 12<br>73 |

|   |                   | 1 0                                                            | 15<br>75 |

|   | 4.3               | ±                                                              | 19<br>78 |

|   | $\frac{4.5}{4.4}$ | ·                                                              | 10<br>30 |

|   | 4.4               | 1                                                              | 30       |

|   |                   | 1 1                                                            | 31       |

|   |                   |                                                                | 35       |

|   |                   |                                                                | 37       |

|   | 4.5               | 9                                                              | 38       |

|   | $\frac{4.5}{4.6}$ |                                                                | 9<br>39  |

|   |                   | 1                                                              | 90<br>90 |

|   | 4.7               |                                                                |          |

|   | 4.8               | ±                                                              | 90       |

|   |                   | _                                                              | 1        |

|   |                   |                                                                | 1        |

|   |                   | 0                                                              | 92       |

|   |                   |                                                                | 93       |

|   |                   |                                                                | 4        |

|   |                   | 4.8.6 Scan Production                                          | 95       |

|   |       | 4.8.7   | Raw Scan Production                         |   | <br> |       |   |       |   | . 9  | 7 |

|---|-------|---------|---------------------------------------------|---|------|-------|---|-------|---|------|---|

|   |       | 4.8.8   | Simple Raw Event Decoding                   |   |      |       |   |       |   |      |   |

|   | 4.9   | Specia  | al Scan Types                               |   |      |       |   |       |   |      |   |

|   |       | 4.9.1   | Configuration Check                         |   |      |       |   |       |   |      |   |

|   |       | 4.9.2   | Pipeline Test                               |   | <br> |       |   |       |   | . 9  | ç |

|   |       | 4.9.3   | Full Bypass Test                            |   |      |       |   |       |   |      |   |

|   |       | 4.9.4   | Noise Occupancy                             |   | <br> |       |   | <br>• |   | . 10 | C |

|   |       | 4.9.5   | Redundancy                                  |   | <br> |       |   | <br>• |   | . 10 | 1 |

|   |       | 4.9.6   | Synchronous Triggers                        | • | <br> |       |   |       |   | . 10 | 2 |

|   | 4.10  | Fitting | g Service                                   | • | <br> |       |   |       |   | . 10 | 3 |

|   |       |         | sis Service                                 |   |      |       |   |       |   |      |   |

|   | 4.12  | Archiv  | ving Service                                | • | <br> |       |   |       |   | . 10 | 4 |

|   | 4.13  | Config  | guration Database                           |   | <br> |       |   |       |   | . 10 | ٥ |

|   |       | 4.13.1  | Module Indexing Schemes                     |   | <br> |       |   |       |   | . 10 | ٥ |

|   |       | 4.13.2  | Implementation                              |   | <br> |       |   |       |   | . 10 | 7 |

|   |       | 4.13.3  | Optimizations                               |   | <br> |       |   |       |   | . 10 | S |

|   | 4.14  | Summa   | nary                                        |   | <br> |       |   |       |   | . 11 | C |

| _ | ~ ~ ~ |         |                                             |   |      |       |   |       |   |      |   |

| 5 |       |         | el Macro-Assembly                           |   |      |       |   |       |   | 11:  |   |

|   | 5.1   |         | out Hardware Configurations                 |   |      |       |   |       |   |      |   |

|   |       | 5.1.1   | Two Module Configuration                    |   |      |       |   |       |   |      |   |

|   |       | 5.1.2   | Configuration of Test Sector                |   |      |       |   |       |   |      |   |

|   |       | 5.1.3   | Configuration for Barrel 3                  |   |      |       |   |       |   |      |   |

|   | 5.2   |         | on Box Set-up                               |   |      |       |   |       |   |      |   |

|   | 5.3   |         | tests                                       |   |      |       |   |       |   |      |   |

|   | 5.4   |         | 3 Testing                                   |   |      |       |   |       |   |      |   |

|   |       | 5.4.1   | Barrel 3 Noise Measurements                 |   |      |       |   |       |   |      |   |

|   |       | 5.4.2   | Closely Separated Triggers                  |   |      |       |   |       |   |      |   |

|   |       | 5.4.3   | Occupancy Per Event Plots                   |   |      |       |   |       |   |      |   |

|   |       | 5.4.4   | Synchronous Trigger Test                    |   |      |       |   |       |   |      |   |

|   |       | 5.4.5   | Barrel 3 Defect Summary                     |   |      |       |   |       |   |      |   |

|   | 5.5   | Conclu  | $usion \dots \dots \dots \dots \dots \dots$ | • | <br> | <br>• | • | <br>• | • | . 13 | U |

| 6 | Pixe  | als     |                                             |   |      |       |   |       |   | 14   | 1 |

| 0 | 6.1   |         | luction                                     |   |      |       |   |       |   |      |   |

|   | 6.2   |         | ation for Design of HEPAPS3                 |   |      |       |   |       |   |      |   |

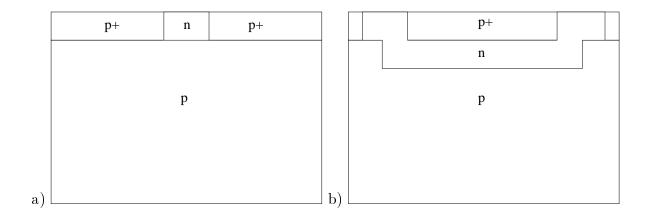

|   | 0.2   | 6.2.1   | Deep n-well Variation                       |   |      |       |   |       |   |      |   |

|   |       | 6.2.2   | 4MOS Variation                              |   |      |       |   |       |   |      |   |

|   |       | 6.2.3   | Enclosed Geometry Variation                 |   |      |       |   |       |   |      |   |

|   |       | 6.2.4   | PMOS Variation                              |   |      |       |   |       |   |      |   |

|   | 6.3   |         | a of HEPAPS3                                |   |      |       |   |       |   |      |   |

|   | 0.0   | O       | Layout of Pixel Test Structures             |   |      |       |   |       |   |      |   |

|   |       |         |                                             |   |      |       |   |       |   |      |   |

|     | 6.3.2  | On-chip Read-out Electronics          |

|-----|--------|---------------------------------------|

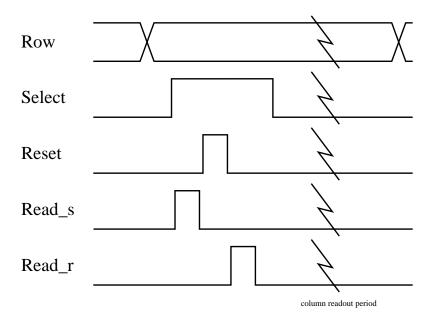

|     | 6.3.3  | Read-out Procedure                    |

|     | 6.3.4  | Silicon Process                       |

| 6.4 | Device | e Testing                             |

|     | 6.4.1  | Source Test Procedure                 |

| 6.5 | Test R | tesults                               |

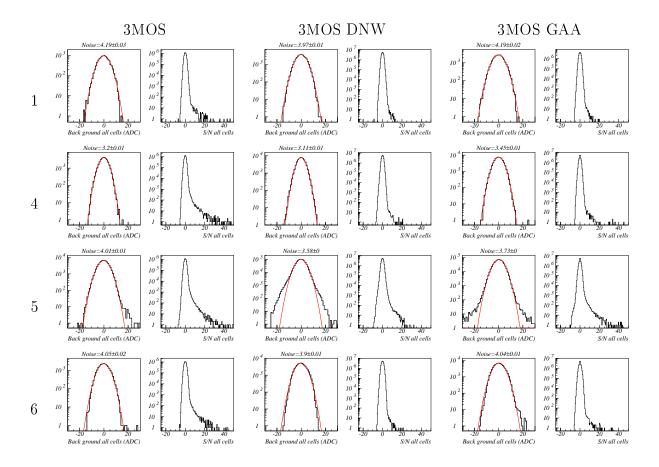

|     | 6.5.1  | Background Noise                      |

|     | 6.5.2  | Cluster Size Histograms               |

|     | 6.5.3  | Signal Histograms and Signal-to-Noise |

| 6.6 | Conclu | ısion                                 |

# List of Figures

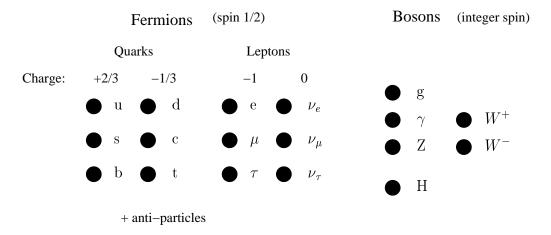

| 1.1  | The standard model particles                                                   | 3   |

|------|--------------------------------------------------------------------------------|-----|

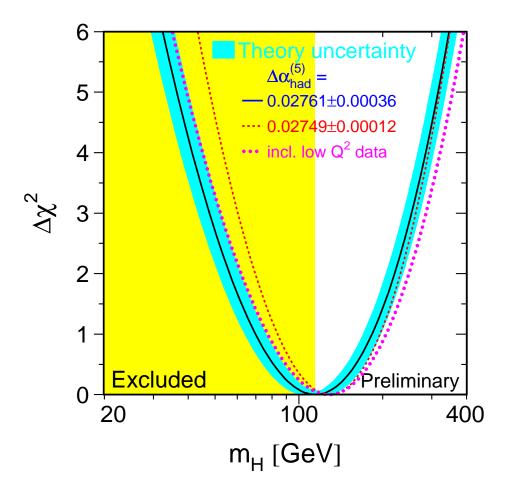

| 1.2  | Constraints on the Higgs mass from LEP measurements                            | 5   |

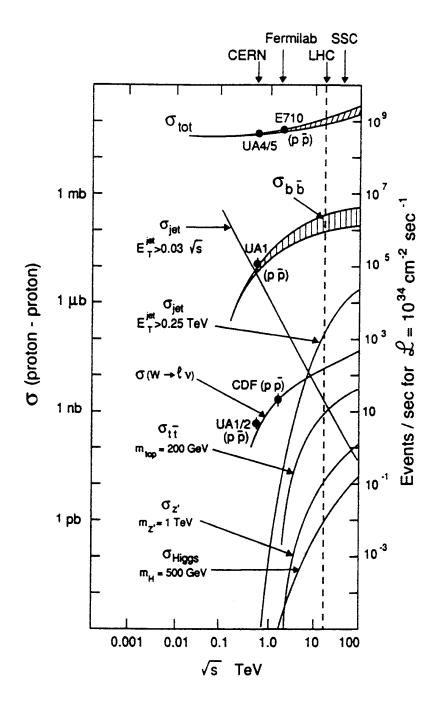

| 1.3  | Cross-sections of p-p collisions as a function of cm energy                    | 7   |

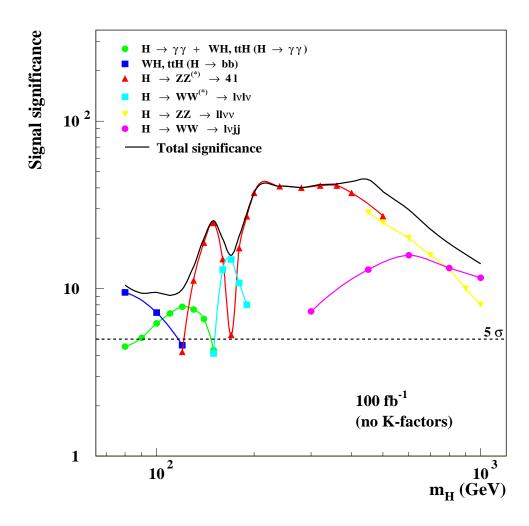

| 1.4  | Potential for discovering the Higgs at ATLAS as a function of Higgs mass .     | 8   |

| 2.1  | Magnetic flux in LHC dipole                                                    | 17  |

| 2.2  | Injector chain for the LHC collider                                            | 18  |

| 2.3  | Octants of the LHC collider                                                    | 19  |

| 2.4  | Schematic diagram of the ATLAS detector                                        | 21  |

| 2.5  | Particle identification by detection in different regions                      | 23  |

| 2.6  | The inner detector                                                             | 26  |

| 2.7  | The calorimeters                                                               | 33  |

| 2.8  | The muon detector, showing the coverage of the different sub-detectors $$ . $$ | 35  |

| 3.1  | Module layout on barrel and endcap                                             | 41  |

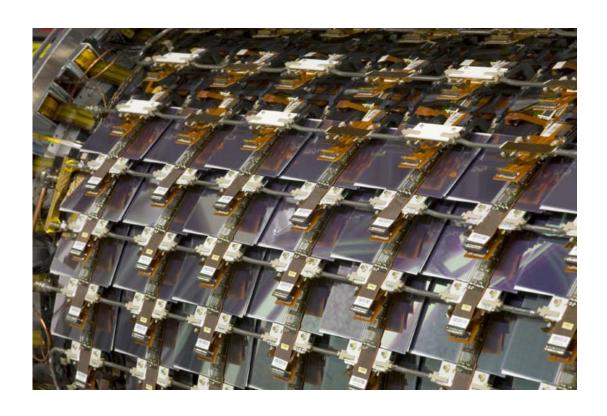

| 3.2  | Photo of modules on barrel 3                                                   | 42  |

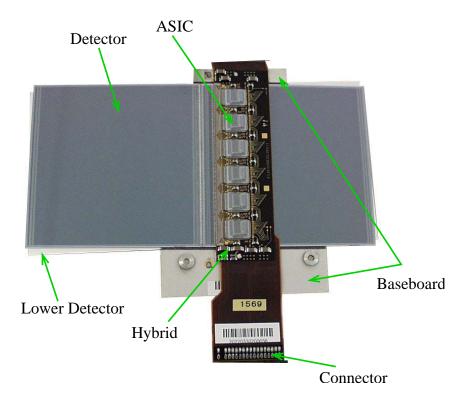

| 3.3  | Picture of barrel module showing various components                            | 47  |

| 3.4  | Picture of the barrel hybrid                                                   | 50  |

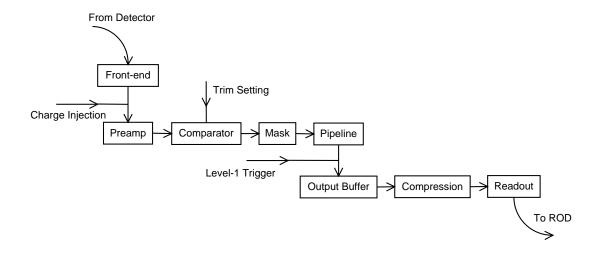

| 3.5  | The components of the ABCD chip                                                | 51  |

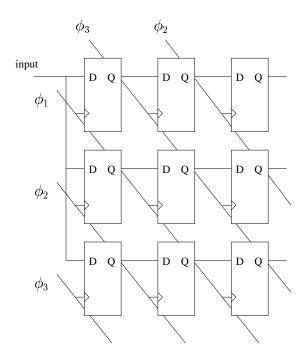

| 3.6  | 3x3 illustration of the pipeline system                                        | 52  |

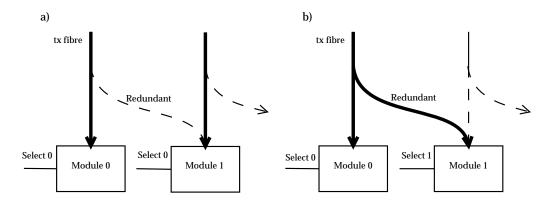

| 3.7  | A pair of modules with redundant connections                                   | 57  |

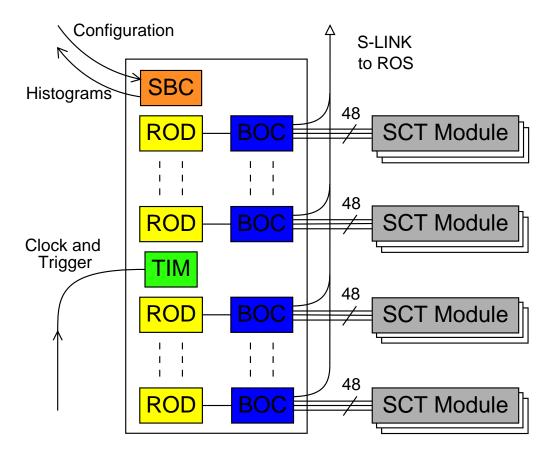

| 3.8  | Scheme of the VME cards in a ROD crate                                         | 58  |

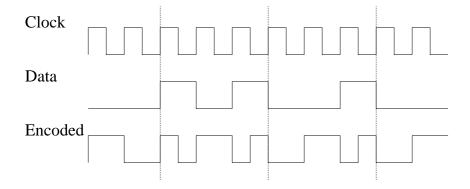

| 3.9  | BPM encoding of the bunch crossing reset signal                                | 60  |

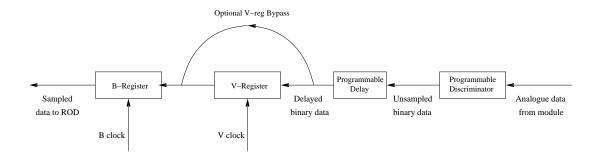

|      | BOC buffers in the RX system                                                   | 61  |

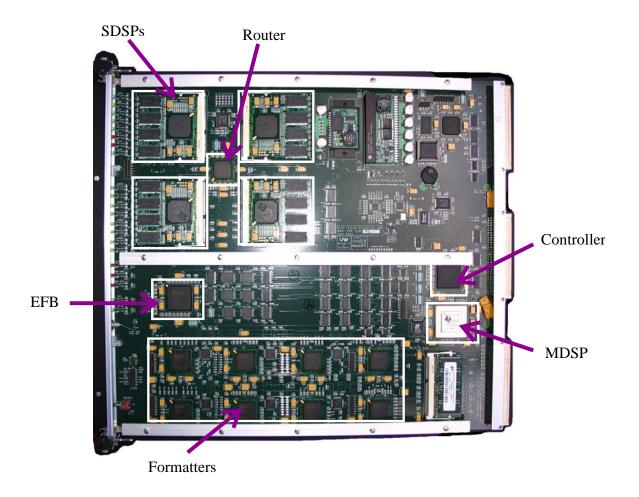

| 3.11 | Picture of ROD module                                                          | 63  |

| 3.12 | The ROD PrimList structure, each line represents a 32bit word                  | 67  |

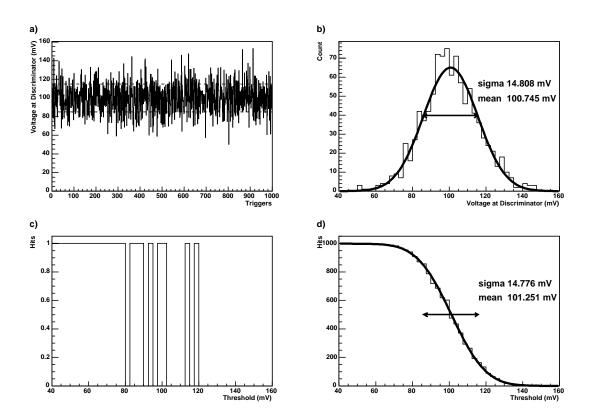

| 4.1  | Simulation showing how detector noise is used for SCT module calibration       | 74  |

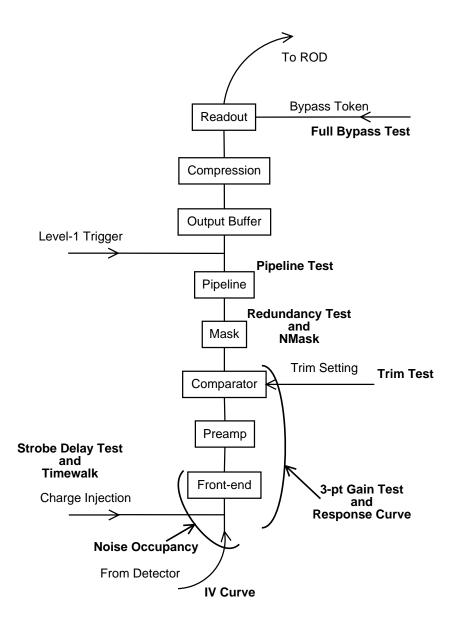

| 4.2  | Overview of module data flow                                                   | 77  |

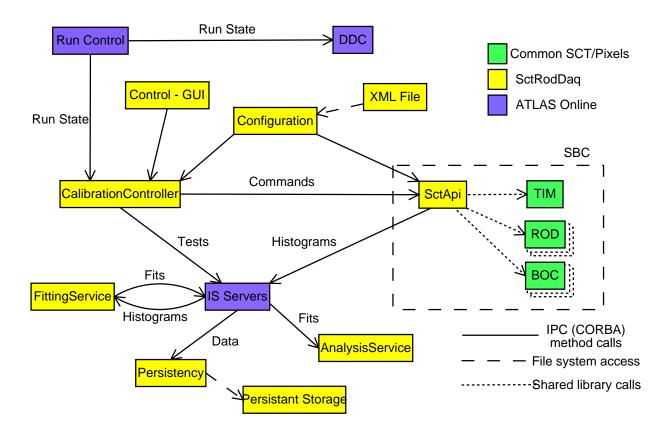

| 4.3  | Overview of elements of SctRodDaq                                              |     |

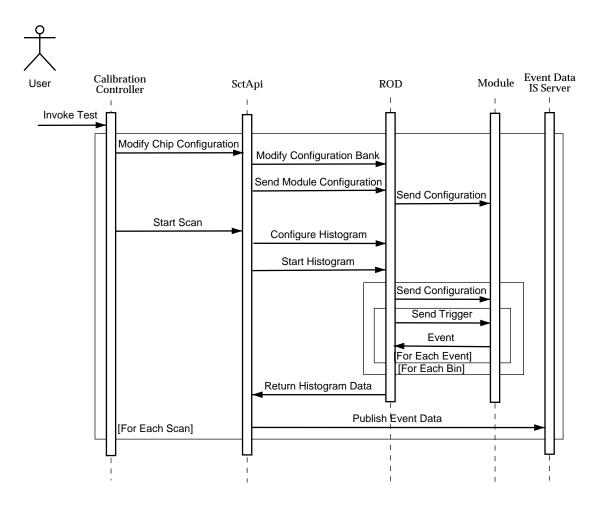

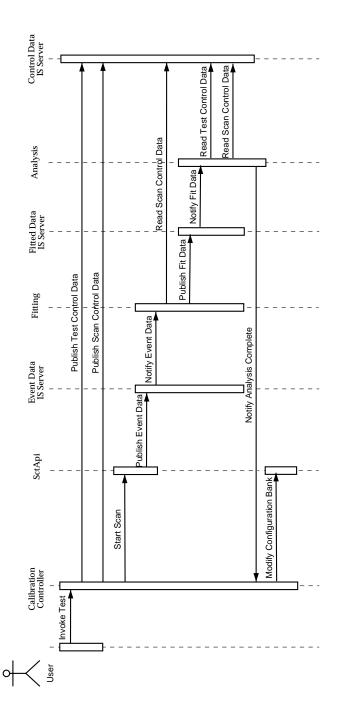

| 4.4  | Sequence diagram showing the production of histogram data                      | 83  |

| 4.5  | Sequence diagram showing processing of histogram data                          | 84  |

| 4.6  | Two modules controlled by two RODs                                             | 101 |

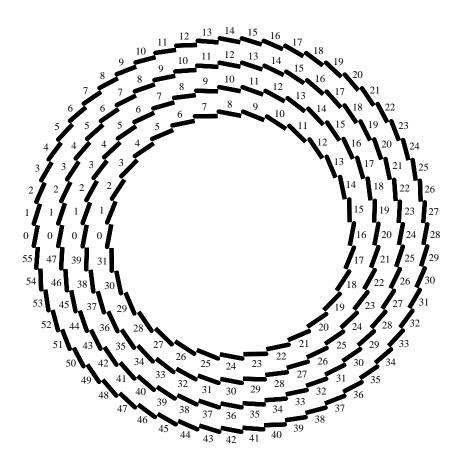

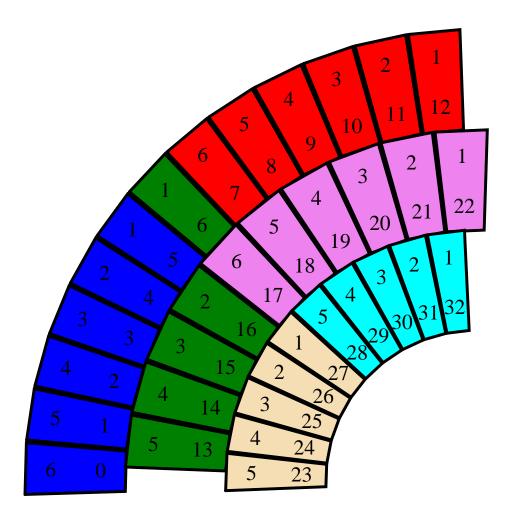

| 4.7  | The row positions on the SCT Barrel                                         | 106  |

|------|-----------------------------------------------------------------------------|------|

| 4.8  | The positions on the SCT End-cap                                            | 108  |

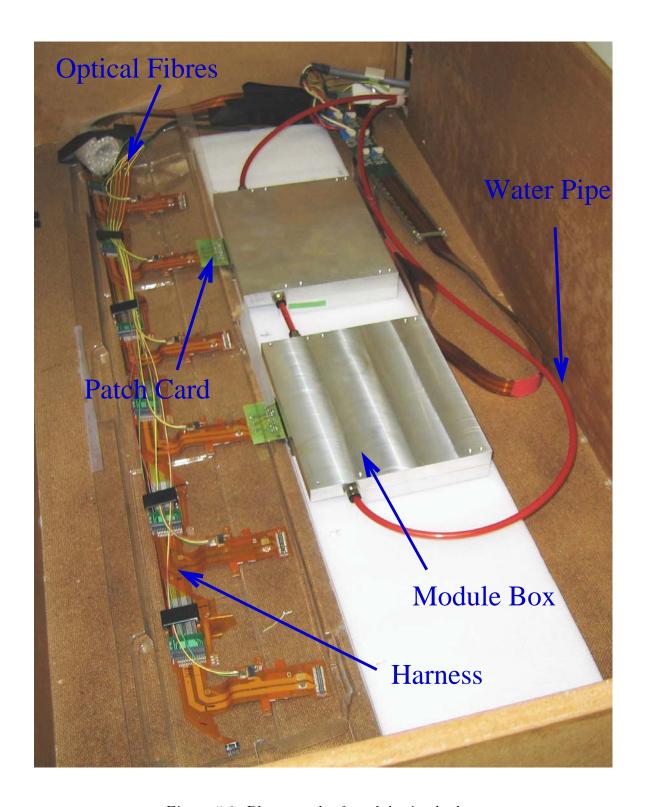

| 5.1  | Photograph of cards in VME crate                                            | 119  |

| 5.1  | Photograph of modules in the box                                            |      |

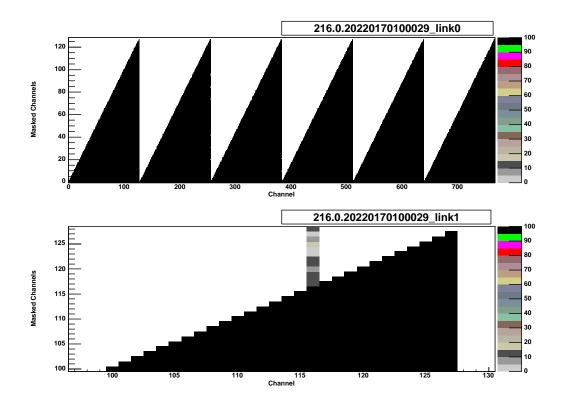

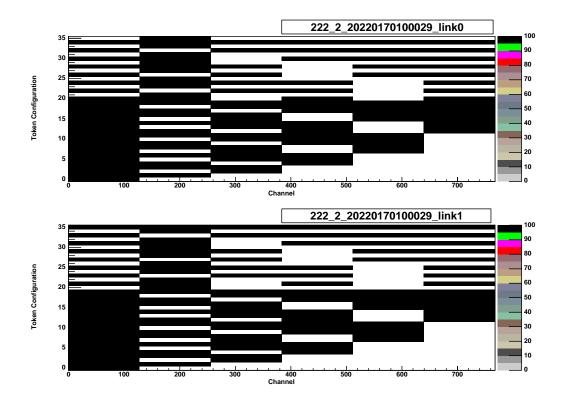

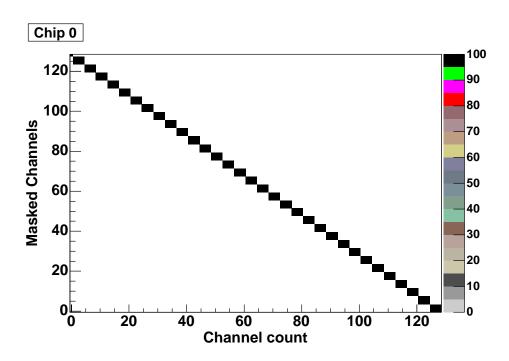

| 5.3  | Plot of an NMask histogram                                                  |      |

| 5.4  | Histogram from a Full-Bypass test                                           |      |

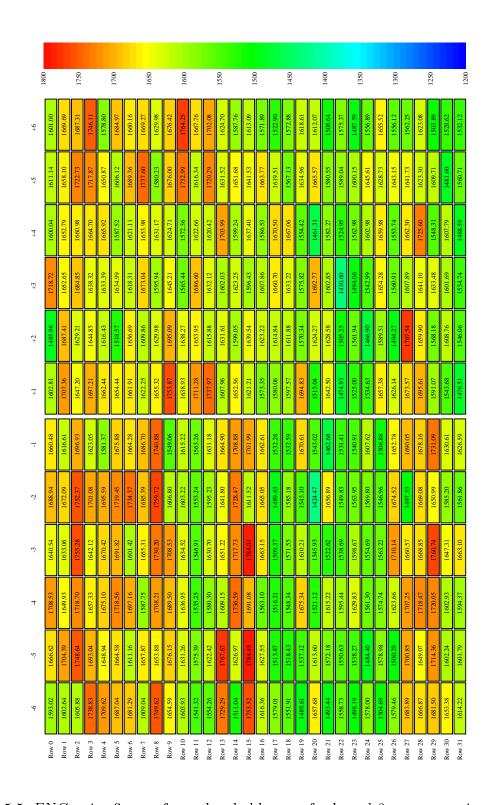

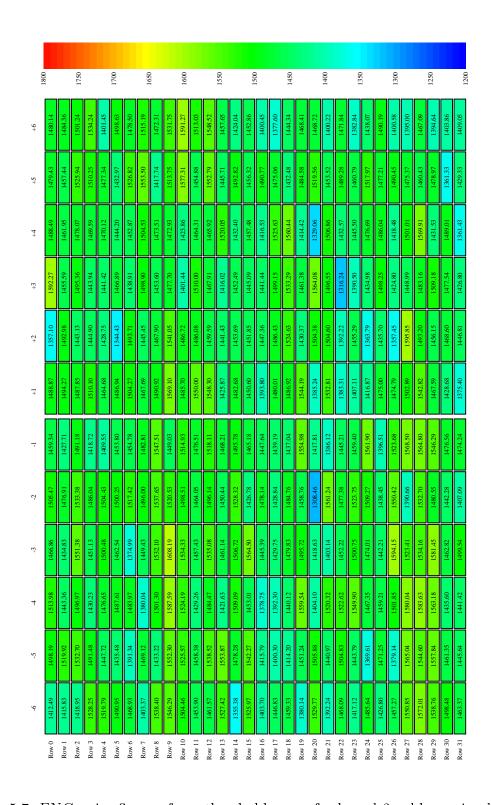

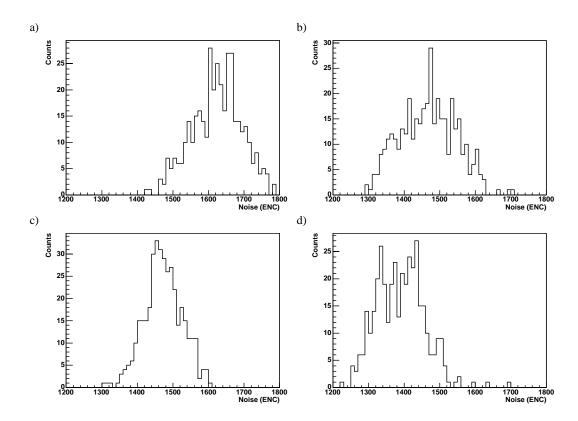

| 5.5  | ENC noise figures from threshold scans for barrel 3 warm run, in electrons  |      |

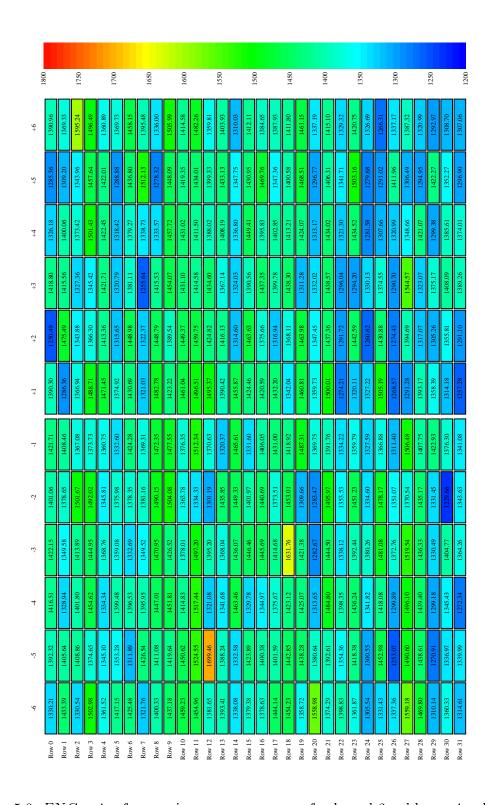

| 5.6  | ENC noise from noise occupancy scan for barrel 3 warm run, in electrons.    |      |

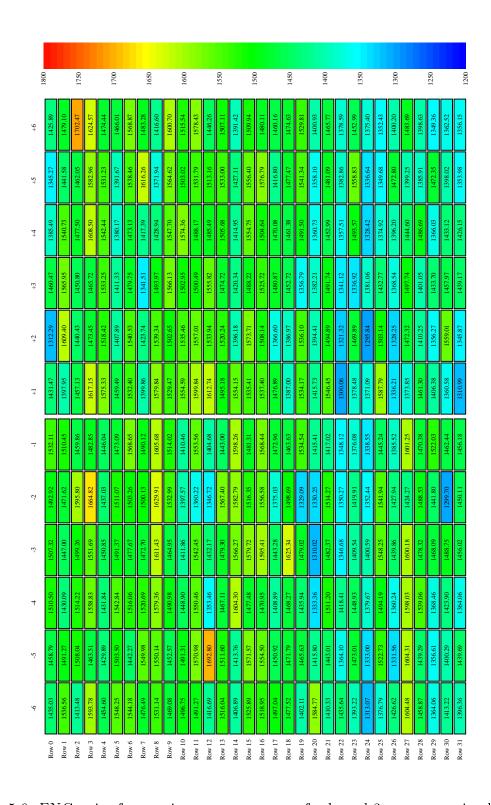

| 5.7  | ENC noise figures from threshold scans for barrel 3 cold run, in electrons. |      |

| 5.8  | ENC noise from noise occupancy scan for barrel 3 cold run, in electrons     |      |

| 5.9  | Comparison of noise histograms                                              |      |

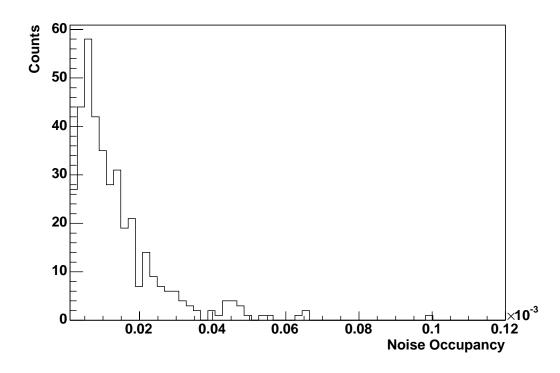

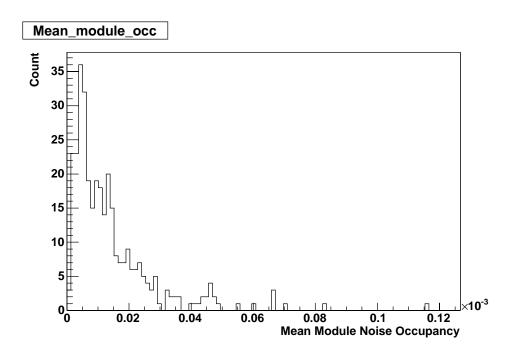

|      | Distribution of mean noise occupancy in the cold run                        |      |

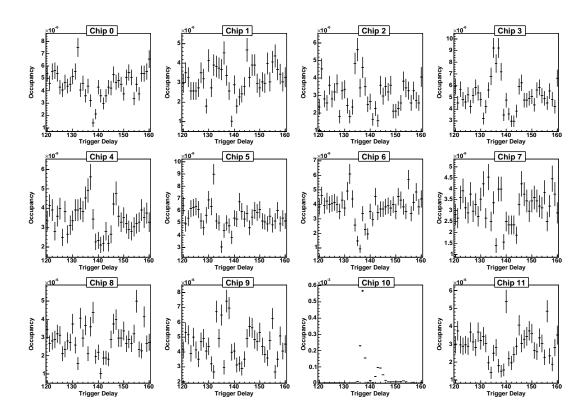

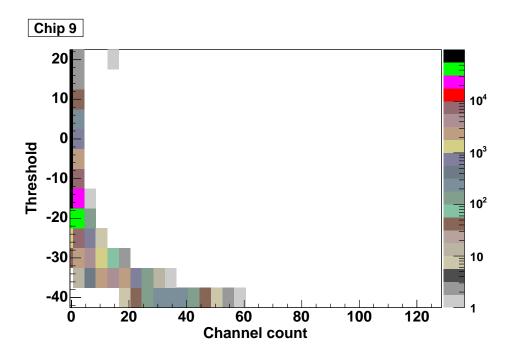

|      | Occupancy histograms per chip from Double Trigger Noise test                |      |

|      | Occupancy plot of the worst module in the Double Trigger Noise test         |      |

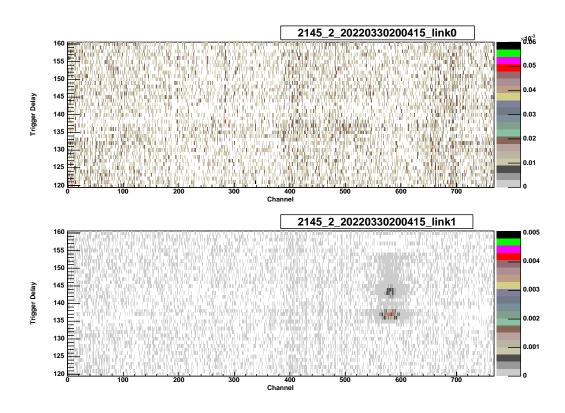

|      | Occupancy per event histogram for a module during an NMask scan             |      |

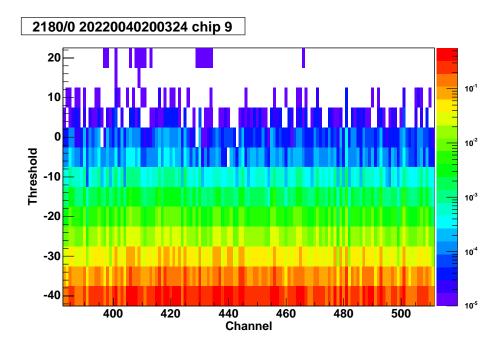

|      | Occupancy histogram of a chip during a Noise Occupancy scan                 |      |

|      | Occupancy per event histogram for a chip during a Noise Occupancy scan.     |      |

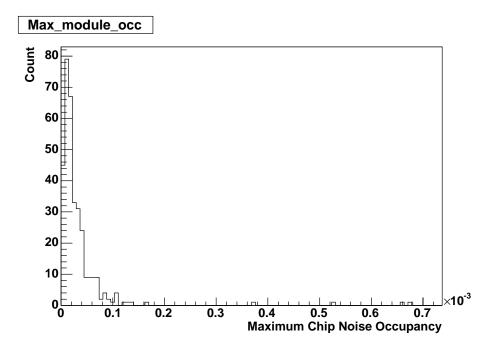

|      | Histogram of mean noise values from synchronous triggers                    |      |

|      | Histogram of maximum noise values from synchronous triggers                 |      |

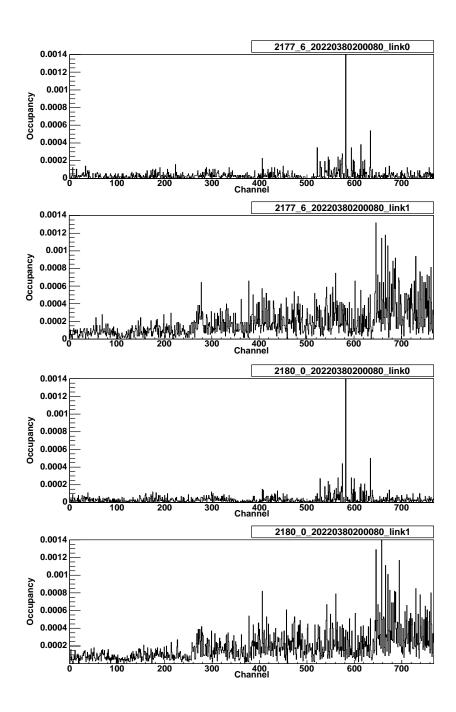

|      | Histograms of a noisy module using synchronous triggers                     |      |

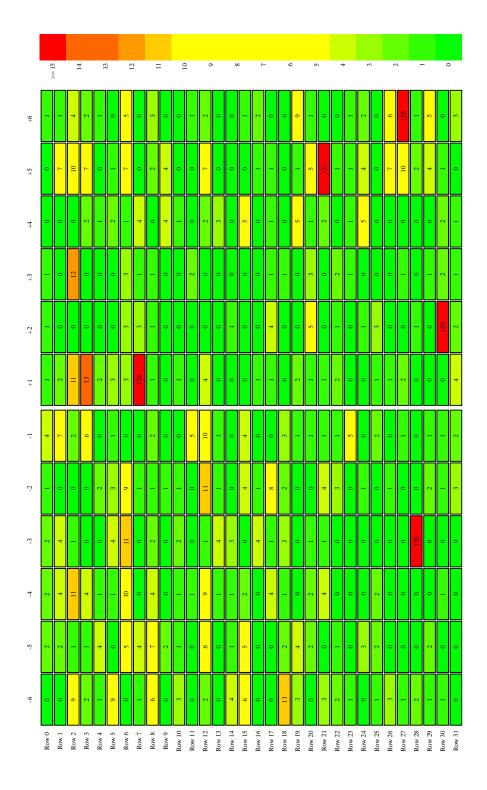

|      | Defective channels for barrel 3 cold run                                    |      |

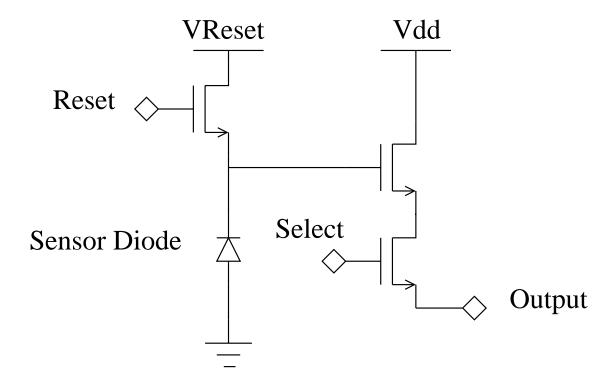

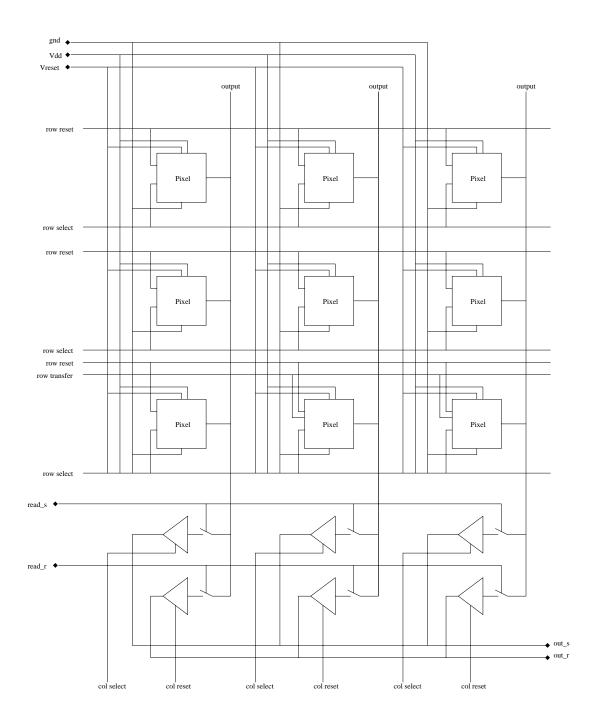

| 6.1  | Schematic of 3MOS pixel                                                     | 1/13 |

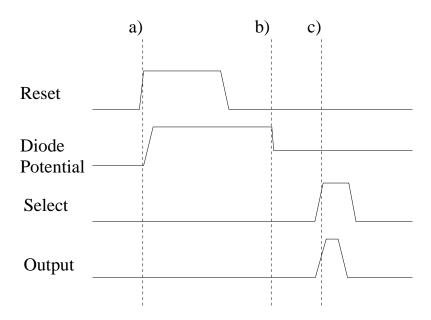

| 6.2  | Timing diagram for 3MOS readout                                             |      |

| 6.3  | Sub-structure of n-well pixel diode                                         |      |

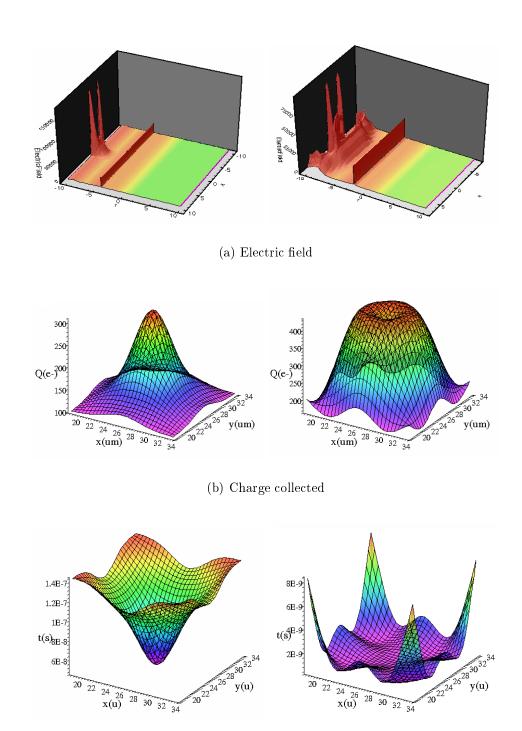

| 6.4  | Simulation of shallow and deep n-well                                       |      |

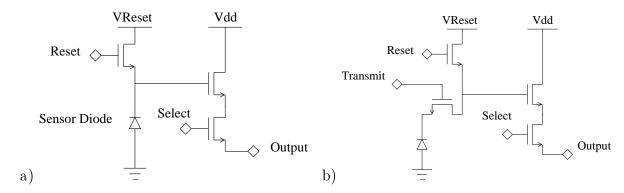

| 6.5  | Schematic of 3 and 4 MOS pixels                                             |      |

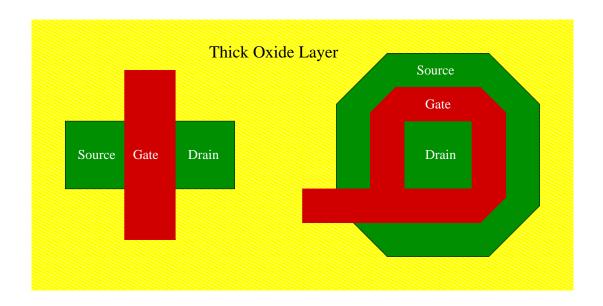

| 6.6  | Layout of standard NMOS and GAA NMOS                                        |      |

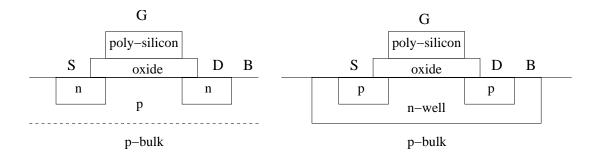

| 6.7  | Cross-sections of standard NMOS and PMOS                                    |      |

| 6.8  | Schematic of readout electronics for HEPAPS3                                |      |

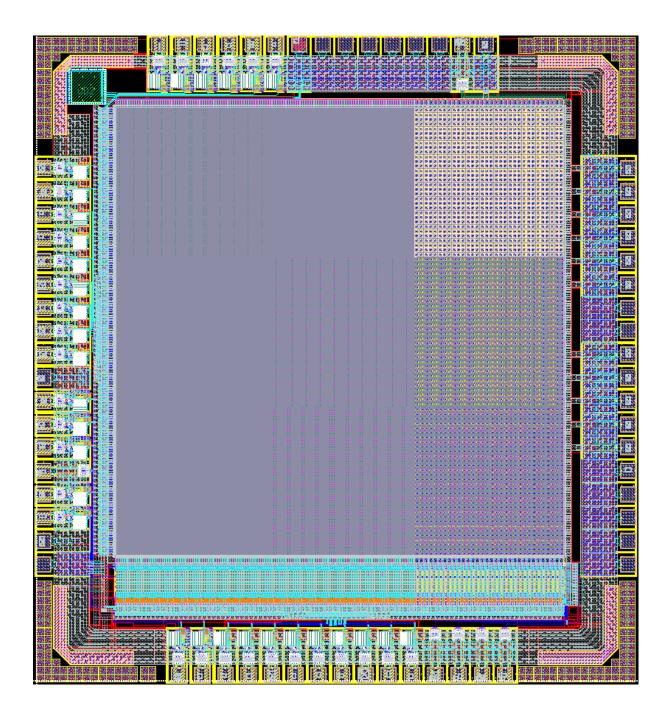

| 6.9  | The HEPAPS3 chip                                                            |      |

| 6.10 |                                                                             |      |

| 6.11 | Distribution of background noise                                            |      |

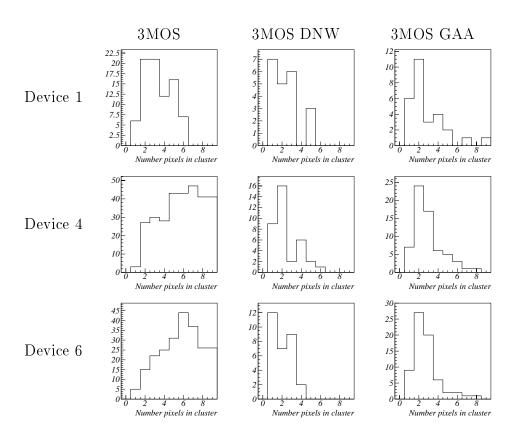

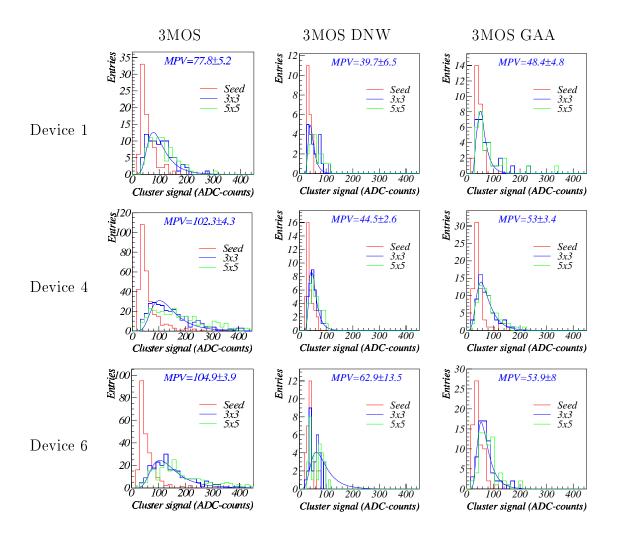

|      | Distribution of cluster sizes for three pixel types in the 3 devices        |      |

|      | Distribution of cluster signals for the 3 devices                           |      |

|      |                                                                             |      |

# List of Tables

| 2.1 | Resolution and Coverage of Inner Detector                                       |

|-----|---------------------------------------------------------------------------------|

| 3.1 | Configuration values for a module                                               |

| 6.1 | Simulation results for standard and deep n-well pixels                          |

| 6.2 | Comparison of pixel types implemented                                           |

| 6.3 | Cluster counts recorded for each device                                         |

| 6.4 | Signal and noise results for the 15 $\mu$ m 3MOS devices                        |

| 6.5 | Signal and noise results for the $15\mu\mathrm{m}$ 3MOS Deep n-well devices 164 |

| 6.6 | Signal and noise results for the $15\mu\mathrm{m}$ 3MOS GAA devices 164         |

|     |                                                                                 |

## Chapter 1

## Introduction

The ATLAS detector is designed to search for the Higgs boson which is predicted to be generated by the LHC collider. It is currently being built and commissioned at CERN on the Swiss-French border. The largest silicon part of the central tracker, the SCT, is being assembled in the UK and this requires testing for quality assurance at all points in the process.

The LHC, ATLAS and the SCT are introduced in chapter 2. This is followed by a more detailed description of the SCT hardware in chapter 3. Chapter 4 introduces the software used for testing and calibration and chapter 5 describes results from tests carried out on the first SCT barrel. Finally, chapter 6 describes some work done towards a next generation silicon detector.

The remainder of this chapter introduces the Standard Model, which describes the particles expected in the ATLAS detector, and how silicon detectors can be used in the detection of the products of collisions in the LHC.

#### 1.1 The Standard Model

The Standard Model of particle physics describes a system of fundamental particles and their interactions. Many predictions of the Standard Model have been tested and found to agree very well with experiment.

The particles can be divided by their spin into three groups: the fermions, 6 quarks and 6 leptons, have spin  $\frac{1}{2}$  † and are responsible for matter, they each have their own antiparticle; the force-carrying bosons, the photon  $(\gamma)$ , W<sup>±</sup>, Z, gluons, have spin 1 and are their own antiparticles; and the Higgs which is discussed further below, it has spin 0 and is unobserved. Figure 1.1 shows a diagrammatical representation of these particles.

The interactions between these particles form into distinct groups according to which bosons are involved. The electromagnetic force is responsible for the everyday forces, electricity and magnetism and is mediated by the photon. The W occurs in short-range weak decays, as in radioactivity. The short range implies a large mass for the W. The gluons bind the quarks into hadrons, pairs in mesons and triplets in baryons. The force is not felt outside the hadron as it is made neutral from the point of view of the colour charge. The most obvious force at scales larger than everyday, gravity, isn't described by the Standard Model but has a negligible effect on the particles and interactions at the smallest scales.

The electro-weak interaction is the result of the unification of electromagnetism and the weak nuclear force. This predicted the Z, which is another massive boson. Its couplings to the fermions are given in terms of the mixing angle  $\theta_W$ . They have been studied in great detail at the LEP collider [1] and found to agree very well with the Standard Model.

These particles and interactions are described by a relativistic quantum field theory. In order that the theory can be used to make physical predictions, a useful feature is its

$<sup>^{\</sup>dagger}\hbar$  and c are taken to be 1 for the remainder of this thesis

Figure 1.1: The standard model particles

renormalisability. It is therefore believed that the theory must also be gauge-invariant, which has been shown to imply renormalisability [2, 3].

The matter around us is made up of u and d quarks - bound into protons and neutrons - and electrons. This means that in order to learn anything about the other particles, we must observe the interactions between these particles and either the particle of interest or its decay products.

The properties of the Standard Model particles have been probed at particle colliders over many years, and all have been observed except for the Higgs. In order to probe for any particle, a machine that collides particles with a centre of mass energy higher than the rest mass of the new particle, is required. This is true of the Higgs which is described in more detail in the following section.

#### 1.1.1 The Higgs Boson

The problem with the currently observed theory, is the difference in mass between the 4 electroweak bosons: the photon has zero mass, the W 80.4 and the Z 91.2 GeV. The zero mass photon arises naturally from the gauge invariant theory for the QED interactions,

but the direct addition of a mass term for the massive bosons will break the symmetry and more seriously the renormalisability of the theory.

An alternative is to add mass to the particles using the mechanism of spontaneous symmetry breaking, where the mathematical formulation remains symmetric, but the physical system prefers a state in which the symmetry is broken.

The Standard Model specifies the Higgs mechanism for breaking the electro-weak symmetry. This introduces a complex doublet of spin 0 particles, three of which are subsumed as the W and Z masses and one which is physically present as the Higgs boson. This mechanism was used to predict the mass of Z from the mass of W:

$$M_W^2 = \rho M_Z^2 cos^2 \theta_W$$

Where  $M_W$  and  $M_Z$  are the masses of the W and Z respectively,  $\theta_W$  is the electroweak mixing angle and  $\rho$  is a correction factor which deviates slightly from 1 for higher order perturbations.

The mass of the Higgs boson is the remaining parameter that predicts all the other properties of the Higgs within the Standard Model. This means that though the mass itself is unknown, for a given mass its behaviour and hence how it may be observed can be fully determined. There are arguments [4] why it should be under 1 TeV and there are previous experiments which would have found a Higgs with a mass below 115 GeV [5]. Figure 1.2 shows the constraints from the LEP experiment: the shaded portion is excluded due to the Higgs not being found directly and the band shows the probable mass based on fits to the Higgs loop correction of the high statistics Z measurements.

In the case that the Standard Model Higgs is not found there are many other theories that have been proposed. A general test for new theories involves measuring interactions where the Higgs is required in the Standard Model. One example is in W-W scattering where, in the absence of the Higgs, the rate of production rises unphysically with increasing

Figure 1.2: Constraints on the Higgs mass from LEP measurements [5].  $\Delta \chi^2$  represents the quality of a fit to the measurements for the different values of  $m_H$

energy.

A popular extension of the Standard Model, which includes the Higgs, involves the introduction of super-symmetry, which adds an additional supersymmetric mirror particle for each currently known particle. The simplest form, MSSM (minimally super-symmetric standard model), has two doublets of complex fields which give rise to 5 Higgs particles, known as A, H, h and H<sup>±</sup>.

#### 1.1.2 Proton-proton Colliders

The LHC is a proton-proton collider. It has advantages in that the energy available in a collision is higher than in previous colliders, as described in section 2.3, but colliding hadrons also introduces unique problems. As the energies used increase, the proton is probed to very small distances. This means the proton can no longer be regarded as a point particle and must instead be regarded as a collection of partons, or the constituent parts of the proton. As a proportion of interactions at high energies, these are mostly gluons and some sea quarks.

The strongly interacting gluons and quarks produce a large number of QCD particles at a much higher rate than any interactions caused by new physics, see figure 1.3. As an example, the total proton-proton inelastic cross-section is estimated as 80mb, in comparison to 120pb for production of a nominal Higgs ( $m_H = 120 GeV$ ). This is a difference of 9 orders of magnitude. Due to this difference, a very large number of collisions are required in order to generate a statistically significant sample of events containing new physics.

Another problem caused by colliding protons is that a large number of hadrons are produced, including many neutrons. This large amount of radiation affects the material used to detect the particles adversely. This is described in section 1.2.4.

Once produced, the Standard Model Higgs will immediately decay into different par-

Figure 1.3: Cross-sections of p-p collisions as a function of cm energy, from [6]

Figure 1.4: Potential for discovering the Higgs at ATLAS as a function of Higgs mass, from [7]

ticles as predicted by the Standard Model and dependent only on the unknown mass. Figure 1.4 shows the discovery potential of the Higgs at the ATLAS detector for the predicted range of masses. This is a function of the branching ratios to the different decay products, the background processes that generate similar decay products and the sensitivity of the ATLAS detector to the decay products. It can be seen that a Standard Model Higgs should be clearly discovered over the mass range 100-1000 GeV.

Many of the decay modes include leptons, which must be reliably distinguished from the hadronic jets. Particularly useful is the ability to distinguish long lived muons. Also, in a decay to neutrinos, the only way to detect them is by measuring the absence of momentum needed to balance that seen in other particles. Decays of b quarks are recognisable by their relatively long life which allows them to travel several hundred microns before decaying further. More information on particle identification in the ATLAS detector in particular is provided in section 2.2.2.

#### 1.2 Silicon Detectors

Particles interact with matter via interactions with either the electrons or nuclei of atoms. The electron field is most likely to be hit if the particle is electrically charged, resulting in ionisation of the material by knocking an electron away from its home atom. In semiconductors, such as silicon, this creates a so called electron-hole pair. The hole represents the absence of an electron and can migrate through the transfer of electrons between atoms.

#### 1.2.1 Interaction of Particles with Matter

The mean energy loss due to ionisation by interactions of charged particles with a material is described by the Bethe-Bloch function [8, 9]. This is written in terms of the charge and speed of the incident particle and also properties of the material in question.

$$-\frac{dE}{\rho dx} = Kz^2 \frac{Z}{A} \frac{1}{\beta^2} \left[ \frac{1}{2} ln \frac{2m_e c^2 \beta^2 \gamma^2 T_{max}}{I^2} - \beta^2 - \frac{\delta}{2} \right]$$

Where K is the constant  $4\pi N_A r_e^2 m_e c^2$ , and  $m_e$ ,  $r_e$ , c,  $N_A$  and K are the standard constants: the mass of the electron, the classical radius of the electron, the speed of light and Avogadro's number respectively. Z, A and  $\rho$  are the atomic number, atomic mass, mass density of the detector material.  $\beta$  is the speed of the incident particle and  $\gamma$  is the Lorentz factor. Finally, z is the amount of charge on the incident particle;  $T_{max}$  is the maximum kinetic energy that can be imparted to a free electron in a single collision; I is the mean excitation energy;  $\delta$  is a correction factor. There are additional correction factors at low energy that are not shown here.

In general, low velocity particles have more time to interact with the material and lose energy quickly. This rate falls as the velocity increases, with  $\frac{1}{\beta^2}$ . It then rises logarithmically, as relativistic effects become prominent, to the Fermi plateau. The minimum is at approximately  $\beta \gamma = 3$  to 4.

The structure of this function gives rise to a relatively well defined point at which the particle minimally excites the material. The energy lost to the material at this point is  $\frac{dE}{\rho dx} \approx 2 MeV cm^2/g$  and a particle with the appropriate energy is referred to as a minimum ionising particle or MIP. This energy loss can be measured by the number of electrons which are ionised, as each electron is ionised by the same amount of energy. A detector can therefore be designed to detect a certain number of electrons, as ionised by the MIP,

and be capable of detecting any other ionising particle which will, by definition, produce more electrons.

The amount of charge liberated by ionisation in a sheet of material for a given incident particle energy is described by the Landau function. This is a distortion of a Gaussian with a long tail towards higher charges, due to the possibility of a small number of particles depositing disproportionately large amounts of energy.

In order to detect the ionisation electrons produced by an incident particle, a detector allows them to migrate in an electric field created by a potential difference across the detector medium. This flow of electrons causes a build up of charge, which can then be measured by supporting electronics.

A common material used for detecting ionising particles is silicon. Its use relies on the semi-conductor properties of silicon and the depletion of free carriers from the silicon using a reverse biased p-n junction, as described in the following.

#### 1.2.2 Silicon Detectors

Silicon is a semiconductor, meaning that the energy gap between the valence and conduction bands is small but not zero (as in a conductor). These have advantages over conductors, in that the small energy gap means an ionising particle can liberate a large number of electrons to be counted. The electrical characteristics of the material can be changed by doping the crystal with group III (eg boron) or V (eg phosphorous) elements. These are called acceptors and donors, respectively, because they lack an electron found in silicon or provide extra electrons to the valence band.

Free carriers are electrons or holes which can move independently of their home atom, in the conduction band. They are liberated by the thermal energy in the material. In doped silicon the majority free carriers are electrons in n-type silicon and they are holes

in p-type silicon.

Once free, electrons and holes migrate due to drift and diffusion. Drift describes movement of charges under the influence of an electric field. Diffusion describes their net movement under random motion which is a function of the density gradient.

#### 1.2.3 p-n Junctions

In order to detect the electron-hole pairs generated by an ionising particle, the signal must be easily detectable above the background, which in this case comes from the collection of the free carriers. Therefore a method of removing as many as possible is required.

A p-n junction is formed at the boundary between the silicon doped with acceptors (p) and that doped with donors (n). In an area either side of the junction, these carriers diffuse across the boundary and recombine with each other, creating a space charge layer in which there is a net positive/negative charge but no free carriers.

The potential difference this creates generates an electric field. This forms a potential barrier which stops most of the current flowing across the junction. This junction behaves as a standard diode; when forward biased, a current flows across the junction. The built-in potential can be increased by reverse biasing the junction, which has the effect of increasing the size of the space charge layer. This is also known as the depletion region due to the absence of free carriers. The remaining current, called the leakage current, is caused by thermally generated pairs which migrate, under the influence of the electric field, across the junction.

#### 1.2.4 Effects of Radiation in Silicon

In addition to the useful ionising interactions with silicon, that enable the detection of particles, there are other interactions, with both temporary effects and long term damaging effects. Temporary upsets are called SEUs (single event upsets) and involve the generation of a large amount of charge in a place other than the detector. This is most likely to manifest itself in an error in the state of digital electronics.

Other effects are caused by the accumulation of defects caused by exposure to many particles. Interactions with the nucleus of an atom can result in displacement of the nucleus within the lattice, or a nuclear reaction which may change the charge of the nucleus.

Displacement of a nucleus results in a vacancy, where the nucleus was, and the interstitial nucleus itself. These can migrate through the crystal lattice and form relatively stable defect complexes, mainly through interaction with impurities in the silicon. These complexes may behave as donors or acceptors, which results in changes in doping type over time. For example, the main part of the SCT detector (see section 3.3.1) is initially n-type sandwiched between more heavily doped p-type silicon at the surface and n-type silicon at the base (p+-n-n+). After irradiation the n-type behaves like p-type so looks like (p+-p-n+). This means that the p-n junction has moved from the top of the wafer to the bottom.

These defects also lead to: increases in the leakage current, ie the current flowing through the junction when no particles are incident; loss of mobility, hence increased recombination and lower charge collection efficiency. Both of these effects lead to a reduction in the signal to noise ratio.

In addition to the detector, transistors in the supporting electronics are also damaged by the radiation. In silicon dioxide, used in the gate oxide of MOS transistors and which is an insulator, displaced electrons and holes, created by ionisation events, drift in the electric field and remain trapped near to the boundary of the material. This has the effect of introducing a fixed charge which affects the behaviour of the transistor. One effect is the reduction in the gate voltage required to turn on a transistor, which can be alleviated by using a thinner gate oxide. Another effect is the creation of parasitic transistors. These are formed around the edges of a transistor through interactions with the oxide that is used to insulate neighbouring transistors. The effect is to change the transistor parameters, including an increase in leakage current. As this is a function of the geometry of the transistor, using a different geometry can help reduce this effect. An example of this is shown in chapter 6.

#### 1.3 Summary

Particle colliders are used to probe the properties of particles. Currently, one of the most interesting particles is the Higgs boson, but very little is known about it. The ATLAS experiment at the LHC collider, described in the next chapter, is designed to investigate this and other particles that might be found at high energies.

One of the materials used to detect the collision products is the semiconductor silicon. This is used both in the SCT strip detector described in chapter 3, and in the experimental HEPAPS3 pixel detector described in chapter 6.

# Chapter 2

## **Detector Overview**

The ATLAS detector is designed to detect the products of collisions in the LHC protonproton collider.

This chapter describes the LHC and ATLAS. It starts with an overview of the LHC accelerator and then of the ATLAS detector. Next, it gives a description of the sub-detectors that make up the ATLAS detector. It ends with the flow of event data from the system.

#### 2.1 LHC

The LHC (Large Hadron Collider) [10, 11] is a 14TeV centre of mass energy proton-proton collider, being installed in the 27km LEP (Large Electron Positron collider) [12] tunnel at CERN. It has almost an order of magnitude higher centre of mass energy than current hadron colliders, the highest energy collider is currently the Tevatron [13] which collides protons and anti-protons with a centre of mass energy of 1.96TeV.

In order to store particles accelerated to a higher energy, either the ring housing the accelerator needs to be bigger, or the magnets used to keep the particles in the ring

must be stronger. Particles in a synchrotron suffer from energy losses due to synchrotron radiation as they are bent. This energy loss increases proportional to  $\gamma^4$ , where  $\gamma$  is the Lorentz factor for the particle. The energy of the LEP e<sup>+</sup>-e<sup>-</sup> collider was limited by these synchrotron radiation losses to a centre-of-mass energy of 210GeV. In the LHC, protons, which are about 2000 times heavier than electrons and therefore have a much lower  $\gamma$  for a given energy, are used instead.

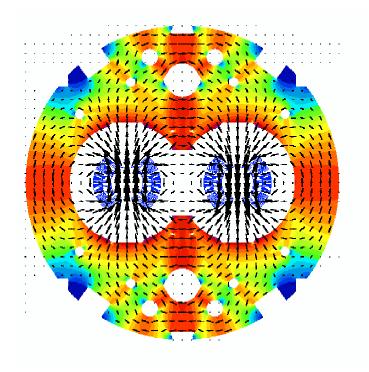

As an alternative to colliding protons with oppositely charged anti-protons, as in previous experiments, the LHC collides two protons. Anti-protons are difficult to create, requiring large numbers of protons to be collided on a fixed target to produce each one, but have the advantage that the oppositely charged beams can be contained in the same magnetic channel. Colliding protons with protons requires the beams to follow two different channels through the bending magnets, with the field in opposite directions in each. In the LHC this is achieved using a complex magnetic field, see figure 2.1, allowing the two beams to be contained in the same magnet.

This enables the same tunnel as the LEP collider to be used with stronger magnets to produce higher energy collisions. The LHC accelerator consists of superconducting magnets, to bend the particles, running all the way around the tunnel, cooled using super-fluid helium to 1.9K.

Another consequence of the increased energy is that, in order to achieve the required event rate to see the low cross-section processes involving high energy particles, the luminosity must be much higher, of the order of  $10^{34}$ cm<sup>-2</sup>s<sup>-1</sup>.

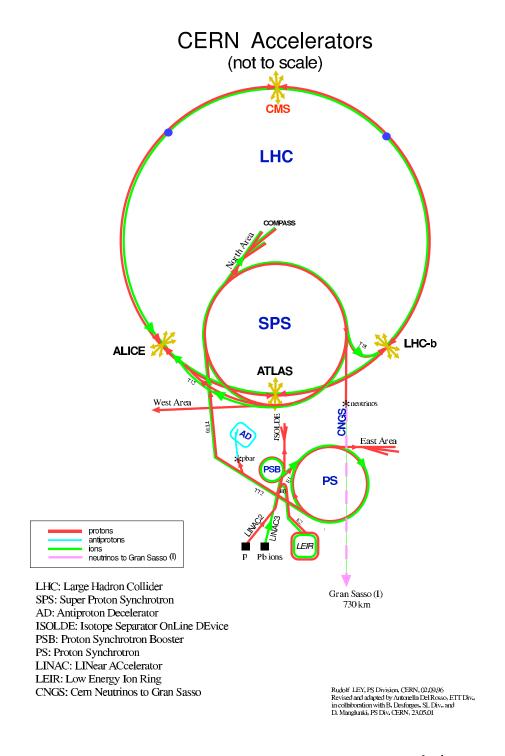

Particles are injected into the LHC by the same injector chain as used for LEP, see figure 2.2. Protons come from the SPS (Super Proton Synchrotron) at 450GeV which come in turn from the PS (Proton Synchrotron) at 26GeV. The protons are initially accelerated by a small linear accelerator and subsequent booster before being injected

Figure 2.1: Magnetic flux in LHC dipole, showing twin cores with opposite field, from [14]

into the PS. The protons are accelerated in bunches which are spaced by 25ns intervals around the LHC ring. This results in the protons in the beams colliding at 40MHz.

Around the LHC ring are 8 straight sections, providing space for other parts of the machine, see figure 2.3. One section contains the RF cavities which accelerate the protons from 450GeV to 7TeV; another holds the beam-dump, where the particles are dumped at the end of a run. Two sections are used to clean the beam of any halo which can form due to unavoidable instabilities in the machine. The remaining four sections are used as interaction points, where the proton beams can be steered and focused on each other to generate collisions. Two general purpose experiments, ATLAS and CMS lie opposite each other. A B-physics experiment (LHCb) and a heavy-ions experiment (ALICE) lie at the interaction points on either side of the CERN main site.

Figure 2.2: Injector chain for the LHC collider, from [15]

18

Figure 2.3: Octants of the LHC collider, from [11]

#### 2.2 ATLAS

ATLAS (A Toroidal LHC ApparatuS) [16, 7] is a detector at interaction point 1 on the LHC ring, closest to the CERN main site. It is a general purpose detector, able to detect the particles expected in Higgs decays and other theories, beyond the Standard Model. One of the key features is its hermeticity, allowing estimates to be made of missing momentum as signatures of neutrinos and other invisible particles. A graphical representation is shown in figure 2.4. The cavern, known as UX-15, to house the detector has been completed and installation of the experiment is underway. Two smaller caverns (US-15 and USA-15) are also present on either side of the LHC ring, where the radiation environment is much less harsh. These are used for services, such as power supplies, cooling and data acquisition.

#### 2.2.1 Co-ordinate system

There are several co-ordinate systems used within ATLAS, depending on context. At a global level, an origin is defined at the nominal interaction point: z describes distances along the beam-pipe; r measures the distance perpendicular to the beam-pipe and  $\phi$  measures angular distance around the beam-pipe. Other co-ordinates are  $\theta$  and  $\eta$ . Firstly,  $\theta$  can be used to describe directly the angle a particle track makes to the beam-pipe, but more usually the pseudo-rapidity,  $\eta$ , is used.

When particles emerge from the collision point, they have components of momentum in both the longitudinal (z) and transverse (r) directions. Rapidity is a Lorentz invariant quantity that is used to combine the two; it is defined as:

$$y = \frac{1}{2} ln \frac{E + p_L}{E - p_L}$$

Where E is the particle energy and  $p_L$  is the longitudinal momentum of the particle. As this quantity varies for a given  $\theta$  with the rest mass of a particle, the pseudo-rapidity

Figure 2.4: A cut-away schematic diagram of the ATLAS detector, from [17]

is used to describe the coverage of the detector. This is is defined as:

$$\eta = -ln[tan(\frac{\theta}{2})]$$

and is equivalent to rapidity for particles with zero rest mass.

#### 2.2.2 Particle Detection

The aim of ATLAS is to detect as far as possible the final state of the proton-proton interaction. This consists of the types of particles that were produced, how much energy they have, and the direction they are travelling. The particles that may be produced consist of the currently known charged leptons, photons, hadrons and neutrinos, and possibly new sorts of stable particles. It is impractical to detect neutrinos, so as an alternative, the momentum balance in the detector is quantified as well as possible.

Some particles produced by the primary event decay very quickly, for example  $\tau$  leptons and B hadrons. In the time taken to decay, a tau lepton may travel of the order of  $100\mu m$  and a B meson as much as 1mm. These may be detected by their decay products as with other short lived particles, but they travel far enough that there is a detectable offset between the original vertex of the subsequent tracks compared to the original vertex of the other collision products, known as a displaced secondary vertex.

Particle tracks are used to discover the momentum of charged particles using a magnetic field. This bends the particles into a helical path where the radius of curvature of the track is proportional to the momentum of the particle. The track can also be used to find the sign of the charge. The energy of both charged and neutral particles are discovered by absorbing them in the calorimeters.

Particle types are mainly distinguished by their differing interactions with matter as shown in figure 2.5: charged particles interact with the material in the tracking regions, ionising the material, thus making them detectable; electrons and photons interact elec-

|                    | Tracker<br>Ionising particles | Ecal<br>Electromagnetic | HCal<br>Hadronic particles | Muons<br>Ionising particles |  |

|--------------------|-------------------------------|-------------------------|----------------------------|-----------------------------|--|

| Photon             |                               |                         |                            |                             |  |

| Electrons          |                               |                         |                            |                             |  |

| Charged Hadrons    |                               |                         |                            |                             |  |

| Neutral<br>Hadrons |                               |                         |                            |                             |  |

| Muons              |                               |                         |                            |                             |  |

| Neutrino           |                               |                         |                            |                             |  |

| 1,000              |                               |                         |                            |                             |  |

Figure 2.5: Particle identification by detection in different regions

tromagnetically with the electrons and nuclei in the denser electromagnetic calorimeter to produce showers of e's and  $\gamma$ 's; hadrons interact strongly with the nuclei of the matter, but at a lower rate than the electromagnetic particles, and particularly in the hadronic calorimeter, finally, muons interact less than the other particles and remain to interact with the muon detectors on the outside of the experiment. Additionally, some particle types can be distinguished based on the velocity of the particle; this enables electrons (with low mass) to be distinguished from other charged particles with a similar momentum.

#### 2.2.3 Triggers

The LHC has a bunch crossing rate of 40.08MHz and a readout of the whole detector contains ~1MB of information. Full readout of the detector at full speed would require a very high bandwidth and an inordinate amount of storage space.

As described in section 1.1.2, the rate of production of particles, such as the Higgs, which are of interest, is very low compared to the background produced by inelastic collisions. As there are identifiable signatures for the interesting particles, it is possible to trigger readout based on these signals and throw away the majority of the data before it needs either bandwidth or storage space. In ATLAS, these signals are such things as high or missing  $P_T$  (transverse momentum), the presence of a muon, or a displaced secondary vertex (signifying production of a b-quark).

ATLAS has three levels in the trigger system, each successive level taking more time to process more of the data in an event in order to cut the event rate.

Only a small part of the detector takes part in the first stage, called Level 1. The final decision to accept the event is made by the Central Trigger Processor (CTP), based on information from specialized parts of the muon chambers and calorimeters. Using this information the event rate can be reduced from 40MHz to a maximum of 75kHz. The decision is made by the trigger processors with a maximum latency of  $1\mu s$ , allowing time for the signal to be distributed among the other detectors in a total of  $2.5\mu s$ . In addition to the decision, the Level 1 trigger specifies Regions Of Interest (ROI), which are sectors of the detector that contain the large energies or muon particles on which the decision was based, and which may be of interest to higher level triggers.

The Level 2 trigger system further reduces the event rate. It has access to data from all the sub-detectors but restricts itself to the particular ROIs that Level 1 specified. Triggers are generated at an average rate of 1kHz with a maximum of 3kHz.

The data corresponding to the Level 2 events is sent to Level 3 (also known as the Event Builder). The Event Builder makes use of all the information from the detector for the specified bunch crossing to take a final on-line decision. Data is then written to disk for off-line analysis at about 200Hz or around 320MB/s.

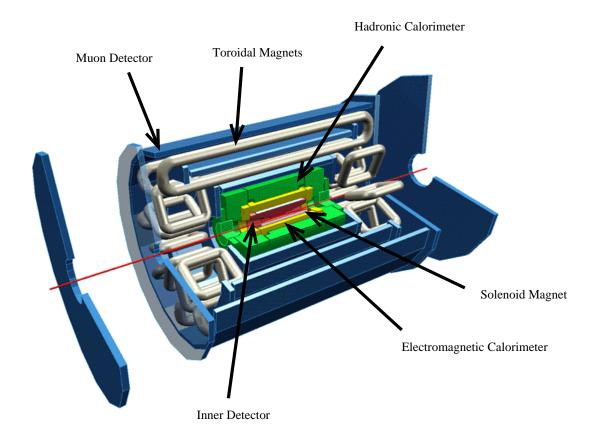

### 2.2.4 ATLAS Overview

The detector itself is arranged in a cylindrical-onion like formation. It is divided into sub-detectors, which use different particle detection methods and most of which have a common barrel and end-cap structure. The barrel measures the positions of particles in  $\phi$  and z at given radii, and the end-cap measures positions in  $\phi$  and r at known z positions. The end-caps enable coverage of a wider range in  $\eta$ , where extending the barrels would provide little useful information.

The different sub-detectors are shown in figure 2.4. At the very centre of the detector is the beam-pipe, where the collisions occur. Next, going outwards, is the Inner Detector, which provides tracking for measuring particle momenta. This is itself divided into three: the silicon vertex detectors, called the Pixel detector; silicon strip detectors, the Semi-Conductor Tracker, and the Transition Radiation Tracker, which is a gas straw tracker.

Surrounding the Inner Detector are the calorimeters. The inner calorimeter measures the energy of electromagnetic particles and a fraction of the energy of the hadrons, the remaining hadronic energy is measured in the second 'hadronic' calorimeter layer.

Finally, muon detectors form an outer shell around the detector, which once again use a tracking system to determine the momentum of the muons, which have passed with only minimal interactions through all the previous detectors, before they escape the detector. This requires a large magnetic field in the muon volume which is provided by the barrel and end-cap toroids.

### 2.3 Inner Detector

The inner detector (ID) [18] is designed for the measurement of charged particles by tracking their positions as revealed by the ionisation of the material. This includes allowing an

| Detector | Position                | $Area/m^2$ | Resolution $\sigma/\mu m$   | Channels/ $10^6$ | $\eta$ coverage |

|----------|-------------------------|------------|-----------------------------|------------------|-----------------|

| Pixels   | B-layer                 | 0.2        | $r\phi = 12, z = 66$        | 16               | $\pm 2.5$       |

|          | $\operatorname{Barrel}$ | 1.4        | $r\phi = 12, z = 66$        | 81               | $\pm 1.7$       |

|          | End-cap                 | 0.7        | $r\phi = 12, r = 77$        | 43               | 1.7 - 2.5       |

| SCT      | $\operatorname{Barrel}$ | 34.4       | $r\phi = 16, z = 580$       | 3.2              | $\pm 1.4$       |

|          | End-cap                 | 26.7       | $r\phi = 16, r = 580$       | 3.0              | 1.4 - 2.5       |

| TRT      | $\operatorname{Barrel}$ |            | 170 per straw (ie $r\phi$ ) | 0.1              | $\pm 0.7$       |

|          | End-cap                 |            | 170 per straw (ie $r\phi$ ) | 0.32             | 0.7 - 2.5       |

Table 2.1: Resolution and Coverage of Inner Detector

Figure 2.6: The inner detector, cut away to show SCT, Pixels and beam-pipe, from [18]

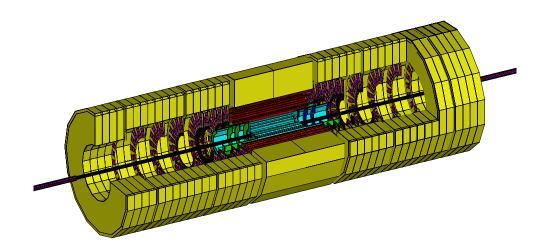

accurate reconstruction of the primary interaction point, and also of displaced secondary vertices. The ID is surrounded by a solenoid, allowing the curvature of the particles in the magnetic field to be used to work out the momentum. This provides a nominal 2T field that bends the particles into a helix. Three different tracking methods were chosen, suited to increasing distances from the beam pipe, they are represented in the three subdetectors of the ID: the Pixels, a silicon vertex detector; the SCT, a silicon strip detector, and the TRT, a transition radiation gas wire tube tracker. The main features of these detectors are shown in table 2.1.

The inner detector is engineered as a whole, see figure 2.6, allowing it to be placed in the detector more easily and also allowing environmental controls to be shared between the three sub-detectors. Both the SCT and TRT barrel sections are contained in a volume of dry  $CO_2$ , which is kept at room temperature. This is the preferred environment for the TRT. Within this volume the SCT is hermetically sealed in a container which is filled with cold (around  $-10^{\circ}$ C), dry nitrogen. The container for the pixel detector is separate so it can be removed independently, and is also filled with cold dry nitrogen.

### 2.3.1 Pixels

The Pixel vertex detector [19] is the innermost ATLAS sub-detector. It records positions of particles with a high spatial accuracy in at least three planes. In the barrel points are recorded in z and  $\phi$  with a fixed r; the end-cap fixes z and records the r coordinate.

The detector is made up from many similar modules. The barrel and end-cap each have a single module design. The support structures are made up of three barrels and three disks at each end. The barrel is made up of two permanent barrels (at radii 9.9 and 12.3cm) with an extra layer of detectors at a very small distance (5.1cm). This layer is especially useful for b-tagging and is referred to as the B-layer. The three disks are placed

at z's of between 11 and 20cm. The B-layer provides the same coverage ( $|\eta| < 2.5$ ) as the remaining detector (both barrel and end-cap), but at a higher resolution.

Due to its close proximity to the beam, the radiation dose received by the pixel layers is extremely large, the inner permanent layer will receive  $1 \times 10^{14} \text{n/cm}^2$  of 1MeV neutron equivalent and 50Mrad of ionising radiation over the 10 year LHC operation. The central B-layer receives 5 times this dose, which has consequences for the life time of this layer and it is designed to be replaced after a few years running.

There are 1456 barrel modules and  $288 \times 2$  end-cap modules each with over 50,000  $50 \times 400 \mu \text{m}$  pixels. In the B-layer the pixels are slightly shorter  $(300 \mu \text{m})$ . Each module covers an area of  $16.4 \text{mm} \times 60.8 \text{mm}$ . Each of 16 chips on each module reads out  $18 \times 160 \text{ pixels}$ .

The modules are based on pairings of detector wafers and readout chips, which are bump-bonded to each other. The wafers are biased to a voltage of around 100V. The first level of readout is carried out in the 16 chips on each module. Each pixel on the detector corresponds to an area in the readout chip which contains an amplifier and discriminator. The information from each pixel is read out by a circuit per column which compresses the binary data (removing the zeros) and stores it while waiting for the level 1 trigger accept. On reception of the level 1 accept signal, a module level chip collects data for a single bunch crossing from the buffers and passes the event data to a control chip for transmission off the detector.

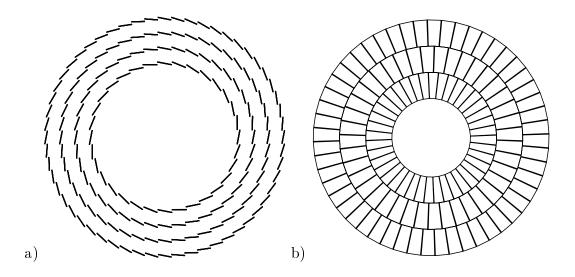

### 2.3.2 Semi-Conductor Tracker

The next division of the inner detector is the SCT silicon strip detector. This provides a balance between the higher resolution of the pixel detector and the need to put as little material as possible before the calorimeters.

The detector medium is a silicon crystal semi-conductor, with embedded strips separated by  $80\mu$ m and biased with a voltage of around 150V. Each module is made up of two pairs of silicon detectors each read out by 6 readout chips, which each read out 128 strips.

The barrel portion of the SCT consists of 2112 barrel modules, covering the rapidity range  $|\eta| < 1.4$ . The modules are arranged on four concentric cylinders, at radii 30, 37.3, 44.7 and 52cm each with 32, 40, 48 and 56 rows of 12 modules respectively.

The end-cap structure is supported by two cylinders, and has 988 end-cap modules divided between 9 discs positioned at each end of the barrel. A fully populated disc contains 132 modules, with 52, 40 and 40 modules in the outer, middle and inner rings respectively. In order to make the most efficient use of silicon area, the modules are arranged such that a particle must travel through four layers of the detector (as with the barrel) and there is minimal coverage above  $|\eta| = 2.5$ . This means that some discs aren't fully populated, where this would introduce extra material for no gain in coverage.

This sub-detector is described in more detail in chapter 3.

### 2.3.3 TRT

The transition radiation tracker is the outermost portion of the inner detector. It is a gas tube tracker. Particles passing through a gas in an electric field generate currents in wires in the centre of the tube (or straw). The barrel straws are oriented axially and layered such that a particle is designed to pass through about 34 straws.

A special feature of the TRT is its ability to distinguish electrons due to their X-ray radiation on transitioning between two media of differing refractive index. This determines the structure of the plastic (polypropylene/polyethylene) surrounding the straws.

A straw is a hollow tube of diameter of 4mm with a  $30\mu m$  W-Re wire through the

centre between which is applied a high voltage (around 1.6kV). The tube is filled with a mixture of 3 gases: Xenon captures the X-rays of the transition radiation, CF<sub>4</sub> increases the gas speed and CO<sub>2</sub> is used to stabilise the mixture in the high electric field. The straws have a relatively small diameter compared to a standard gas detector. This is due to the very high hit occupancy that would result if the straws were a few centimetres across.

The straws are arranged with 50,000 axial straws in the barrel and 160,000 radial straws in each end-cap. A measurement of the drift-time across the tube enables space point measurements in  $\phi$  with a resolution of 170 $\mu$ m per straw. In order to avoid excess occupancy where the coverage is already very good, the first few layers of the barrel aren't active in the central portion. All the barrel straws are divided at z=0 and read out at each end, the end-cap straws are read out at the outer end.

A large part of the read-out electronics for the TRT deals with the precise cancellation of the response from the Xenon gas. This takes microseconds to decay, compared to the several nanosecond timing precision and recovery needed. The generation of the artificial response is carried out using RC filters.

### 2.3.4 Track Reconstruction

Tracks are fitted to space-points which are gathered from the hit information in the Inner Detector, allowing reconstruction of the path the particle took. The track follows a decaying helical function defined by the momentum and pseudo-rapidity of the object particle and also the strength of the magnetic field used.

The particle momentum is proportional to the radius of curvature of the track: for a normally incident particle, the momentum of a particle is given by p = 0.3BR, where p is momentum in GeV, B is the magnetic field in T and R is the radius in m [9]. The error

in the curvature k = 1/R of the track due to the resolution of the measurement can be approximated by:

$$\delta k_{res} = \frac{\epsilon}{L'^2} \sqrt{\frac{720}{N+4}}$$

though this calculation is approximate for small N (< 10) and the accuracy is also affected by multiple scattering, particularly at low momenta. The track length in m is L', N is the number of measurements and  $\epsilon$  is the measurement error in m.

The momentum resolution is therefore directly related to the accuracy and resolution of the space-point measurements and this argument motivates the very high resolution necessary in the inner detector. The precision of ID measurements allow measurements of particle momenta up to hundreds of GeV.

## 2.4 Calorimetry

Outside the tracking of the inner detector, the next layers are the calorimeters. These measure the energies of the incident particles. Two types of calorimeter are used, the electromagnetic calorimeter which wholly absorbs the lightest electromagnetically interacting particles,  $\gamma$ ,  $e^-$ ,  $e^+$ , and usually contains part of any hadronic showers. The hadronic calorimeter absorbs essentially all of the remaining strongly interacting particles, leaving only muons and neutrinos, of the known Standard Model particles, to escape the detector.

The principle of operation is similar in both sections of the detector. The incident particle interacts with a shower material or absorber, producing a shower of secondary particles, which are sampled in a detecting material. Two methods are used for detection: liquid argon in a high electric field produces cascades of electrons which are detected as charge and read out electrically; the tile calorimeters use a scintillating plastic which

generates visible photons which are detected using photo-multiplier tubes. The size of the signal is approximately proportional to the incident particle energy, in both cases a calibration is made based on known particle energies.

Electrons, photons and hadrons interact with matter in different ways: the first two interact with electrons and the electric fields around the nuclei in the detector. The distance travelled before interaction is usually measured in radiation lengths. Hadrons interact via strong interactions with the nuclei in the detector. In this case, the distance travelled is usually measured in interaction lengths. The typical distance travelled in the detector before interaction for hadronic particles is longer than for electrons and photons, which enables the different shower types to be distinguished.

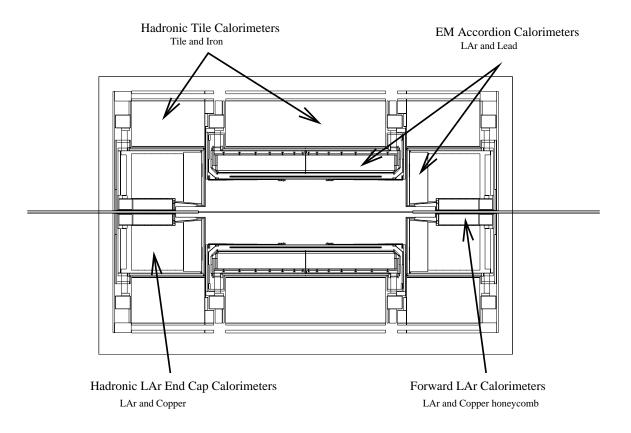

The ATLAS calorimetry is sub-divided into different systems, covering different pseudorapidity ranges and differing depending on the required resolution and particle type and also the prevailing radiation conditions. The subsystems are shown in figure 2.7 and described below.

## 2.4.1 Electromagnetic Calorimeter

The electromagnetic calorimeter is constructed from alternating layers of lead and liquid argon samplers, in an "accordion" geometry, such that gaps between detector modules are minimised.

A pre-sampler is placed in the barrel ( $|\eta| < 1.8$ ), to allow corrections to be made for pre-showering within the inner detector volume. The remainder of the detector is built to sample showers created in the absorber layers.

The calorimeter is divided into cells which point towards the interaction region. This enables the measurements to be directly translated into  $\eta$  and  $\phi$ .

Figure 2.7: The calorimeters, adapted from [20]

### 2.4.2 Hadronic Calorimeter

The hadronic calorimeter is divided into portions that use LAr as the active medium, as in the EM calorimeter, and a scintillator tile based detector.

The barrel section ( $|\eta| < 1.7$ ) is made up of an iron absorber, with plastic tile scintillator plates. This does not have a high radiation hardness and so a different technology is used in the end-cap.

The hadronic end-cap, covering  $1.5 < |\eta| < 3.2$ , works similarly to the electromagnetic system, detecting the shower using liquid argon as the active medium and uses copper as the passive shower material.

The forward calorimeter provides coverage in the extreme pseudo-rapidity region,  $3.1 < |\eta| < 4.9$ , where no other detectors are placed. This is a high radiation environment so there is a need for an intrinsically radiation hard system. Holes of diameter 5mm are formed in a block of copper or tungsten and rods of diameter 4.5mm are inserted. LAr is used as the active medium in the  $250\mu m$  gap formed in-between.

Instead of pointing towards the interaction region, the hadronic calorimeter cells have a similar cross-section for all z in the barrel and in the end-cap. In order to provide data on jets in the barrel in  $\eta$  and  $\phi$ , the cells are grouped as inputs to the PMTs. The end-cap cells already provide symmetry in  $\phi$  and are formed into groups of similar  $\eta$ .

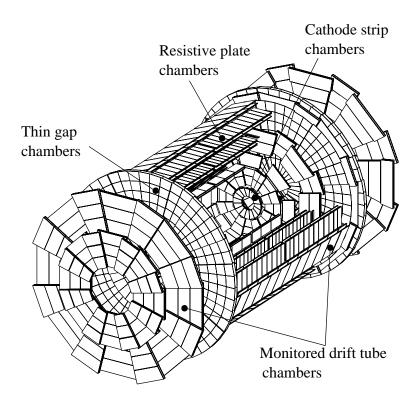

## 2.5 Muon Detector

The muon detector [21] measures the presence of, and finds the momentum of, the remaining detectable particles, muons. It is made up of several parts, the most visible being the external magnets which provide a toroidal field in order to bend the remaining particles to reveal momentum information.

Figure 2.8: The muon detector, showing the coverage of the different sub-detectors (from [22])

Within the magnetic field the muon detectors are divided into different types, as shown in figure 2.8. The monitored drift tube chambers (MDTs) measure the precise co-ordinate, required for momentum measurements, in both the barrel and end-cap. They are complemented by the cathode strip chambers (CSCs) in the very high  $|\eta|$  region. The muon detector also provides input to the level 1 trigger decision. This information is provided by the resistive plate chambers (RPCs) in the barrel and the thin gap chambers (TGCs) in the end-cap. They also provide positional information orthogonal to the momentum measurement. These detector types are described briefly below.

### **2.5.1** Toroids

Surrounding the whole experiment are the muon toroid magnets, which cause the tracks of the muon particles to bend in order to allow the determination of muon momenta. The magnets create a toroidal field running around the detector, therefore particles are bent such that the angle made with the beam-pipe changes. This is in contrast to the magnetic field of the inner detector and means that momentum resolution in the muon detectors is determined by the precision measurement of z in the barrel and r in the end-caps.

The toroidal field is created by 8 toroids in the barrel, which are air cooled superconducting magnets 26m long with an outer diameter of 20m. In the end-cap 8 toroids are rotated by 22.5 degrees so they fit in the end of the barrel toroids. They extend 5m from the calorimeter barrel and have inner and outer diameters of 1.65m and 10.7m respectively. These can be seen in figure 2.4.

### 2.5.2 Detector Chambers

The precision momentum measurements are supplied mainly by the MDT (monitored drift tube) detectors. These are drift tubes of 30mm diameter, with a central  $50\mu$ m W-Re wire separated by a potential of 3kV. A timing resolution of 300ps over a maximum drift time of 500ns gives an average positional accuracy of  $80\mu$ m per wire. The "monitored" in the name of the detector refers to optical imaging scans that measure the alignment of the detector a few times an hour. In order to provide the required accuracy, the position of the wires must be known to within  $50\mu$ m. The drift tubes are supported by rigid cross-plates at either end, but the longest tubes are around 6m long and mechanical deformations of the order of  $10\mu$ m are expected due to thermal effects, gravity and torsion.

The CSCs (cathode strip chambers) are located in the extreme end-cap (2.0 <  $|\eta|$  < 2.7), where the predicted hit occupancy would be too high for the MDT system. These

are gas drift chambers with a 2.6kV bias. The cathodes are separated by 5.08mm, with anode wires separated by 2.54mm running through the centre. A precision measurement (r) is provided by measuring the charge recorded on neighbouring cathode strips, which are orthogonal to the wires and read-out at a pitch of 5mm. This system allows a track resolution of  $60\mu$ m.

The barrel trigger functionality is provided by the RPCs (resistive plate chambers). These are formed from resistive plates surrounding gas chambers, with a high voltage (9kV) applied across the 2mm gap. Orthogonal strips with a pitch between 30 and 40mm on each side of the gap allow a capacitive readout. The strips are read out digitally giving a typical space-time resolution of 1cm×1ns.

In the end-cap the trigger functionality is provided by the TGCs (thin gap chambers). A gas-filled chamber of width 2.8mm contains central anode wires separated by 1.8mm. A voltage of 3.2kV is applied across the gap. To match the required momentum resolution for the low precision trigger signals, groups of between 4 and 20 wires are connected together. Orthogonal read-out strips with a pitch between 15 and 50mm are capacitively coupled to the cathode and are read out to provide precision measurements of the  $\phi$  component to complement the r component measured by the MDT.

## 2.6 The ATLAS Data Acquisition System

Data Acquisition, or DAQ, is the process of reading out the event data from the detector. In ATLAS it is strongly linked to the trigger system [23] described in section 2.2.3. Level 1 trigger information is gathered via a fast path for low resolution data from both the calorimeters and the muon trigger chambers. It is then processed rapidly to produce sufficient information for the decision.

The remainder of the detector must meanwhile buffer the data so it will still be avail-

able on reception of the Level 1 trigger accept decision, up to  $2\mu$ s after the bunch crossing. In different sub-detectors this is implemented in different ways, but the data for the event corresponding to the Level 1 trigger bunch crossing must be available to the Level 2 trigger.

All the signals from the on-detector electronics chips leave the sub-detectors and are transmitted to off-detector electronics systems, mainly housed in two smaller caverns, US-15 and USA-15, either side of the main ATLAS cavern. Here the radiation levels are much lower and general purpose electronics can be used.

The TTC (Timing, Trigger and Command) system is used to distribute to the sub-detectors the L1 accept (L1A) trigger signal, the 40MHz bunch crossing clock and global resets of bunch crossing and event counters in order to keep the whole detector synchronized. This is done using a hierarchy of TTC crates which distribute the information to the sub-detector specific ROD (Read-out driver) crates in a standard format.

The first level of off-detector read-out is performed in the ROD crates. The RODs are sub-detector specific boards which convert signals directly from the sub-detectors into a common ATLAS event format. This data is then transmitted via a standard interface called the S-LINK [24]. The ROS (Read-Out Sub-system) receives the data from the sub-detectors, buffered by the ROB (Read-Out Buffer) and responds to requests for events from the Level 2 trigger systems and the event builder. The event builder is responsible for building complete events, from the portions provided by the sub-detectors, for processing by the event filter.

Once copied to persistent storage the events are available for off-line analysis. This takes place in a distributed manner, data being distributed to sites around the world in a hierarchical tier system. The provision of much of the infrastructure for this is the responsibility of the LCG (LHC computing grid). LCG also provides a database